### Tecnológico Nacional de México

Coordinación Sectorial Académica Dirección de Estudios de Posgrado e Investigación

# Centro Nacional de Investigación y Desarrollo Tecnológico

Subdirección Académica

Departamento de Ingeniería Electrónica

# TESIS DE MAESTRÍA EN CIENCIAS

Evaluación de una Topología para la Alimentación de LED´s de Potencia con Factor de Potencia Alto y Procesamiento Parcial de la Energía

presentada por

Ing. Benito Rodriguez Nava

como requisito para la obtención del grado de Maestro en Ciencias en Ingeniería Electrónica

Director de tesis **Dr. Mario Ponce Silva**

Codirector de tesis

Dr. Carlos Aguilar Castillo

Cuernavaca, Morelos, México. Marzo de 2016.

Cuernavaca, Mor., 25 de febrero de 2016.

OFICIO No. DIE/058/2016 Asunto: Aceptación de documento de tesis

#### DR. GERARDO VICENTE GUERRERO RAMÍREZ SUBDIRECTOR ACADÉMICO

Por este conducto, los integrantes de Comité Tutorial del C. Benito Rodriguez Nava con número de control M14CE32 de la Maestría en Ciencias en Ingeniería Electrónica, le informamos que hemos revisado el trabajo de tesis profesional titulado "Evaluación de una Topología para la Alimentación de LED's de Potencia con Factor de Potencia Alto y Procesamiento Parcial de la Energía" y hemos encontrado que se han realizado todas las correcciones y observaciones que se le indicaron, por lo que hemos acordado aceptar el documento de tesis y le solicitamos la autorización de impresión definitiva.

DIRECTOR DE TESIS

Dr. Mario Ponce Silva Doctor en Ciencias en Ingeniería Electrónica

Cédula profesional 3516427

CODIRECTOR DE TESIS

**REVISOR 2**

Dr. Carlos Aguilar Castillo

Doctor en Ciencias en Ingeniería Electrónica Cédula profesional 3581040

REVISOR

Dr. Jaine Eugenio Arau Rottiel Doctor en Ciencias en Ingenieria Electrónica REV. FOLIO B 045431

Dr. Marco Antonio Oliver Salazar

Doctor en Ciencias en Ingeniería Electrónica Cédula profesional 6526083

Lic. Guadalupe Garrido Rivera.- Jefa del Departamento de Servicios Escolares.

Estudiante

Expediente

CMAZ/Irr

Interior Internado Palmira S/N, Col. Palmira. C.P. 62490 Cuernavaca, Mor. Tels. (01)777 362-77-70 Ext. 4106, e-mail: direccion@cenidet.edu.mx www.cenidet.edu.mx

TECNOLÓGICO NACIONAL DE MÉXICO Centro Nacional de Investigación y Desarrollo Tecnológico

> Cuernavaca, Mor., 25 de febrero de 2016 OFICIO No. SAC/132/2016

Asunto: Autorización de impresión de tesis

ING. BENITO RODRÍGUEZ NAVA CANDIDATO AL GRADO DE MAESTRO EN CIENCIAS EN INGENIERÍA ELECTRÓNICA PRESENTE

Por este conducto, tengo el agrado de comunicarle que el Comité Tutorial asignado a su trabajo de tesis titulado "Evaluación de una Topología para la Alimentación de LED's de Potencia con Factor de Potencia Alto y Procesamiento Parcial de la Energía", ha informado a esta Subdirección Académica, que están de acuerdo con el trabajo presentado. Por lo anterior, se le autoriza a que proceda con la impresión definitiva de su trabajo de tesis.

Esperando que el logro del mismo sea acorde con sus aspiraciones profesionales, reciba un cordial saludo.

**ATENTAMENTE**

"CONOCIMIENTO Y TECNOLOGIA AL SERVICIO DE MEXICO"

DR. GERARDO VICENTE GUERRERO RAMÍREZ SUBDIRECTOR ACADÉMICO CENTRO NACIONAL DI INVESTIGACION Y DESARROLLO TECNOLÓGICO SUBDIRECCIÓN ACADEMICA

C.p. Lic. Guadalupe Garrido Rivera.- Jefa del Departamento de Servicios Escolares. Expediente

GVGR/mcr

Interior Internado Palmira S/N, Col. Palmira. C.P. 62490 Cuernavaca, Mor. Tels. (01)777 362-77-70 Ext. 4106, e-mail: direccion@cenidet.edu.mx www.cenidet.edu.mx

# Agradecimientos

A Dios por iluminar mí camino en los momentos difíciles y por conocer a personas maravillosas.

Al Centro Nacional de Investigación y Desarrollo Tecnológico (CENIDET) por darme la oportunidad de cursar mis estudios de Maestría. Así mismo agradezco el apoyo a quienes laboran en esta gran institución y en especial a Lorena y Anita.

Al Consejo Nacional de Ciencia y Tecnología (CONACYT) por el apoyo económico otorgado para realizar mis estudios de Maestría.

A mis padres Benito Rodriguez Martínez y Ema Nava Linares y mis hermanos René, Daniela y Alonzo por su apoyo en esta etapa de mi vida.

A mis compañeros de generación y otras del área de Electrónica de Potencia, y en especial a Nicolás Torres Cruz porque hicimos un gran equipo de trabajo, prácticamente es como un hermano.

A mi asesor el Dr. Mario Ponce Silva por darme la oportunidad de ser su tesista, sus consejos y paciencia me ayudaron en mi crecimiento profesional.

A mis revisores, Dr. Jaime Eugenio Arau Roffiel, Dr. Marco Antonio Oliver Salazar y coasesor Dr. Carlos Aguilar Castillo por sus observaciones y contribuciones que enriquecieron este trabajo de tesis.

A los profesores que me impartieron clases, Dr. Jesús Aguayo, Dr. Hugo Calleja, Dr. Abraham Claudio, Dr. Luis Gerardo Vela, Dr. Marco Antonio Oliver, Dr. Mario Ponce y Dr. Carlos Aguilar que en su momento compartieron su conocimiento y experiencias.

#### Resumen.

El uso de LEDs para aplicaciones de iluminación ha ido en incremento debido a su eficacia lumínica y tiempo de vida útil. Generalmente los LEDs al igual que las lámparas fluorescentes, HID, inducción, etc., tienen una fuente de alimentación que cuando se conectan a la red eléctrica deben cumplir la norma IEC61000-3-2 clase C. Los LEDs no solo requieren de una fuente de alimentación que cumpla las normas, además debe tener un tiempo de vida útil cercano al del LED. Respecto al tiempo de vida útil se tiene identificado que los capacitores electrolíticos determinan la durabilidad de un fuente de alimentación, para esto ya existe una solución, y es utilizar capacitores de polipropileno que son más costosos con respecto a los capacitores electrolíticos, entonces, para quienes están trabajando en el área, el reto es hallar una topología que haga uso de capacitores de polipropileno cuya capacitancia sea lo más baja posible y con un menor número de elementos electrónicos, esto fue lo que motivó a trabajar en el tema de este trabajo de tesis.

De lo anterior, se evaluó una topología resultado de hacer variaciones de conexión del primario y secundario de un convertidor flyback no aislado. De lo consultado en la literatura para aplicaciones de iluminación HID y fluorescentes, hacer una reconexión estratégica del primario y secundario del convertidor flyback se obtienen beneficios como son: mayor eficiencia, cumplimientos de las normas en cuanto a calidad de la energía y menor porcentaje de potencia procesada por el flyback. Para verificar a qué punto se obtienen estos beneficios para aplicaciones de iluminación LED, se aplicó el Análisis Promediado de Baja Frecuencia APBF.

Posteriormente se planteó como hipótesis obtener los beneficios reportados en aplicaciones de iluminación HID y fluorescente al reacomodar los devanados de un flyback, pero ahora con aplicaciones LED.

De la topología propuesta se probó de manera teórica y experimental que cumple con los requerimientos de la norma IEC61000-3-2 clase C. En pruebas experimentales se reportó una eficiencia de 89% y una potencia procesada por el flyback de 63%. De lo obtenido, se dio por aceptada la hipótesis planteada, menor porcentaje de potencia procesada por el flyback, alta eficiencia comparada con topologías reportadas en la literatura y cumplimiento de las normas. En cuanto al valor de la capacitancia no se logró que fuera menor con respecto a lo que utilizan otras topologías.

En este trabajo de tesis no solo trabajó una topología que no está reportada en la literatura, adicionalmente se desarrolló una metodología para un mejor seguimiento del APBF probando su efectividad en resultados experimentales.

#### **Abstract**

The use of LEDs for lighting applications has gone in increase due to its light efficacy and time of useful life. Generally the LEDs as the fluorescent lamps, HID, induction, etc., have a FA, which when they get connected to the electrical network they must fulfill the norm IEC61000-3-2 class C. The LEDs not only need of a FA that fulfills the norms, also it must have a time of useful life near to that of the LED. With respect to time life has identified that filters determine the durability of a FA, for this a solution already exists, and is use capacitors of polypropylene which are more expensive with respect to the capacitors electrolytic, then, for those who are working in the area, the challenge is to find a topology that makes use of capacitors of polypropylene with a capacitance is as low as possible and with a less number of electronic elements, this was what motivated to work on the topic of this thesis work.

From the foregoing, in this thesis one topology for LED's power supplies was proposed and evaluated, This topology is the result of variations of connections between the primary and secondary of a flyback converter not isolated. This idea already has been presented in the consulted literature for lighting applications, specifically for HID and fluorescent lamps. Whit the strategic reconnection of the primary and secondary of the flyback converter it is possible to obtain benefits such as: greater efficiency, compliance with the standards in terms of quality of energy and lower percentage of power processed by the flyback. To verify the possibilities of these ideas when they are applied to lighting LED, one Low Frequency Averaged Analysis APBF was performed and the analysis presented in this work.

The main hypothesis for this work is to evaluate experimentally the proposed topology in order to assess the benefits reported in previous applications of HID and fluorescent lamps which one resembled the windings of a flyback to increase their efficiency but now with applications LED.

The proposed topology was tested in theoretical and experimental way to comply with the requirements of the standard IEC61000-3-2 class C. The experimental tests reported an efficiency of 89% and the power processed by the flyback was only 63% of the nominal power Therefore, the hypothesis was verified since with this topology the flyback converter processes a lower percentage than in other topologies and high efficiency is obtained too. In terms of the value of the capacitance is not achieving that outside lower as compared to what they use other topologies.

This thesis work presents a different topology that it is not reported in the literature. The analysis of this topology and the development of a design methodology were also presented the experimental results confirmed the good operation.

# Índice

| Resum    | en.                                                                | v  |

|----------|--------------------------------------------------------------------|----|

| Índice ( | de Figuras.                                                        | ix |

| Índice ( | de Tablas                                                          | X  |

| Nomen    | clatura                                                            | X  |

| Acróni   | mos.                                                               | xi |

| Capítul  | o 1. Introducción                                                  | 1  |

| 1.1      | Antecedentes                                                       | 1  |

| 1.2      | Planteamiento del problema.                                        | 2  |

| 1.3      | Estado del Arte                                                    | 2  |

| 1.4      | Propuesta Solución.                                                | 4  |

| 1.5      | Hipótesis.                                                         | 4  |

| 1.6      | Objetivos                                                          | 4  |

| 1.7      | Justificación                                                      | 4  |

| Capítul  | o 2. Análisis de la topología propuesta                            | 5  |

| 2.1      | Modelos de trabajo para el APBF.                                   | 5  |

| 2.2      | Metodología para el APBF.                                          |    |

| 2.3      | Evaluación de la topología.                                        | 8  |

| 2        | 3.1 Evaluación del contenido armónico de corriente "THDi"          | 11 |

| 2.3      | 3.2 Evaluación del factor de potencia "FP".                        | 13 |

| 2.3      | Evaluación del porcentaje de potencia procesada por el flyback "Q" | 13 |

| 2        | 3.4 Evaluación de la eficiencia total " $n_T$ ".                   | 15 |

| Capítul  | o 3. Implementación y pruebas experimentales.                      | 16 |

| 3.1      | Cálculo de los elementos de la topología                           | 16 |

| 3.2      | Resultados en baja frecuencia "Ideal".                             |    |

| 3.3      | Resultados en simulación y pruebas experimentales                  | 18 |

| 3        | 3.1 Medición de " <i>THDi</i> ".                                   | 20 |

| 3        | 3.2 Medición del "FP"                                              | 21 |

| 3        | 3.3 Medición del voltaje en la lámpara LED                         | 21 |

| 3        | 3.4 Medición de la corriente en la lámpara LED                     | 23 |

| 3.3.5          | Medición de la potencia consumida por la lámpara LED.            | 24 |

|----------------|------------------------------------------------------------------|----|

| 3.3.6          | Resumen y porcentajes de error de implementación de la topología | 25 |

| 3.3.7          | Comparativa de topologías.                                       | 26 |

| Capítulo 4. Co | onclusiones y recomendaciones.                                   | 28 |

| Bibliografía   |                                                                  | 29 |

| Anexos         |                                                                  | 31 |

| Sección A1     |                                                                  | 32 |

| Sección A2     |                                                                  | 33 |

| Sección A3     |                                                                  | 34 |

| Sección A4     |                                                                  | 35 |

# Índice de Figuras.

| Figura 1.1. Flyback reacomodado para aplicaciones de iluminación HID                      | 3  |

|-------------------------------------------------------------------------------------------|----|

| Figura 1.2. Flyback reacomodado para aplicaciones de iluminación fluorescente.            |    |

| Figura 1.3. Topología propuesta.                                                          |    |

| Figura 2.1. Modelo del flyback en MCD para el APBF                                        | 5  |

| Figura 2.2. Modelo del LED para el APBF.                                                  |    |

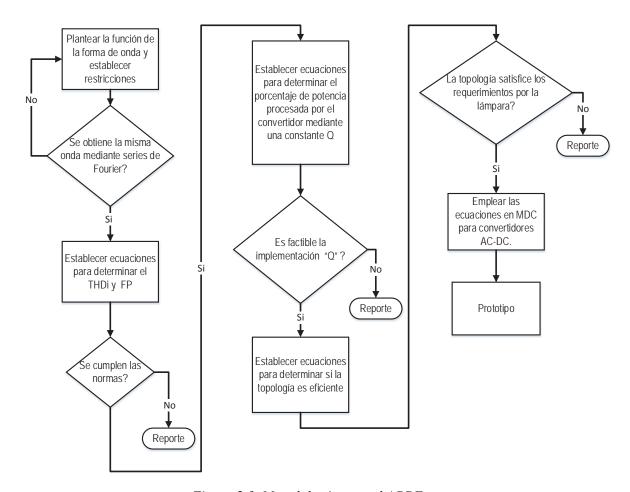

| Figura 2.3. Metodología para el APBF                                                      |    |

| Figura 2.4. Formas de onda vac y vr.                                                      |    |

| Figura 2.5. Esquemático de la topología propuesta y su esquema en baja frecuencia         |    |

| Figura 2.6. Esquema simplificado en baja frecuencia de la topología.                      |    |

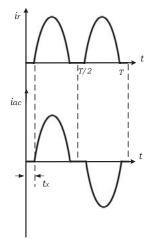

| Figura 2.7. Formas de onda de ir y de iac de la topología                                 |    |

| Figura 2.8. Forma de onda de ir de la topología en Maple.                                 |    |

| Figura 2.9. Forma de onda de iac de la topología en Maple                                 |    |

| Figura 2.10. Forma de onda de iac de la topología en PSIM.                                |    |

| Figura 2.11. THDi de la topología                                                         |    |

| Figura 2.12. Lado izquierdo, curvas de armónicos de la topología y lado derecho           |    |

| requerimientos IEC-61000-3-2 clase C.                                                     | 12 |

| Figura 2.13. FP de la topología.                                                          |    |

| Figura 2.14. Esquemas de flujos de potencia, a) flyback básico y b) flyback reacomodado   | 14 |

| Figura 2.15. Porcentaje de potencia procesada por el flyback "Q"                          | 14 |

| Figura 2.16. Eficiencia total de la topología                                             | 15 |

| Figura 3.1. Lámpara LED construida con LEDs SAW0LH0A                                      | 16 |

| Figura 3.2. Gráfico ampliado de THDi de la topología.                                     |    |

| Figura 3.3. Esquemático de la topología implementada en PSpice                            |    |

| Figura 3.4. Prototipo de la topología para pruebas experimentales                         |    |

| Figura 3.5. THDi obtenido en simulación PSpice.                                           |    |

| Figura 3.6. THDi obtenido en pruebas experimentales del medidor de la calidad de energía. |    |

| Figura 3.7. FP obtenido en simulación PSpice.                                             |    |

| Figura 3.8. FP obtenido en pruebas experimentales por el medidor de la calidad de energía | 21 |

| Figura 3.9. Voltaje instantáneo en simulación de la lámpara LED.                          | 22 |

| Figura 3.10. Voltaje instantáneo en pruebas experimentales de la lámpara LED              | 22 |

| Figura 3.11. Corriente instantánea en simulación de la lámpara LED.                       | 23 |

| Figura 3.12. Corriente instantánea en pruebas experimentales de la lámpara LED            |    |

| Figura 3.13. Potencia instantánea en simulación de la lámpara LED.                        |    |

| Figura 3.14. Potencia instantánea en pruebas experimentales de la lámpara LED.            |    |

| Figura 3.15. Distribución de la potencia manejada por la topología implementada           | 25 |

| Figura 3.16. Formas de onda de corriente suministrada a una lámpara LED de la topología   |    |

| desarrollada por [4]                                                                      | 26 |

# Índice de Tablas.

| Tabla          | 1.1. Comparativa de topologías consultadas en la literatura.                                                                                  | 2     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Tabla          | <ul><li>3.1. Especificaciones técnicas de la lámpara LED de prueba.</li><li>3.2. Cálculo de constantes y elementos de la topología.</li></ul> | 16    |

|                | 3.3. Resultados en baja frecuencia.                                                                                                           |       |

|                | 3.4. Resúmen y porcentajes de error en implementación de la topología                                                                         |       |

| Tabla          | 3.5. Comparativa de topologías de la literatura y la implementada                                                                             | 26    |

| Nom            | nenclatura                                                                                                                                    |       |

| ΔPRF           | Análisis Promediado en Baja Frecuencia.                                                                                                       |       |

| D              | Ciclo de trabajo del convertidor flyback.                                                                                                     |       |

| F              | Frecuencia de conmutación del convertidor flyback.                                                                                            |       |

| FA             | Fuente de Alimentación.                                                                                                                       |       |

| FI             | Fuente de Iluminación.                                                                                                                        |       |

| iac            | Corriente de línea alterna.                                                                                                                   |       |

| Io             | Corriente promedio de salida del convertidor flyback.                                                                                         |       |

| ir             | Corriente instantánea rectificada.                                                                                                            |       |

| Lp             | Inductancia del Primario del flyback.                                                                                                         |       |

| L <sub>p</sub> | Inductancia del secundario del flyback.                                                                                                       |       |

| M              | Ganancia para análisis de convertidores en alta frecuencia.                                                                                   |       |

| m              | Ganancia para análisis de convertidores en baja frecuencia.                                                                                   |       |

| N              | Relación de transformación.                                                                                                                   |       |

| $\eta_F$       | Eficiencia del flyback.                                                                                                                       |       |

| $\eta_T$       | Eficiencia Total.                                                                                                                             |       |

| PFi .          | Potencia promedio de entrada del convertidor flyback en baja frecuencia.                                                                      |       |

| PFo            | Potencia promedio de salida del convertidor flyback en baja frecuencia.                                                                       |       |

| Pi             | Potencia promedio de entrada del sistema.                                                                                                     |       |

| PLam           | Potencia promedio de la lámpara                                                                                                               |       |

| Po             | Potencia promedio de salida del lado secundario del flyback en alta frecuencia.                                                               |       |

| q              | Constante que relaciona a RD y RF.                                                                                                            |       |

| $\dot{Q}$      | Constante que representa el porcentaje de potencia procesada por un convertidor                                                               | •     |

|                | flyback.                                                                                                                                      |       |

| RD             | Resistencia del modelo del LED.                                                                                                               |       |

| RF             | Resistencia libre de pérdidas que representa el primario del flyback.                                                                         |       |

| VD             | Fuente de voltaje de CD del modelo del LED.                                                                                                   |       |

| VF             | Fuente de voltaje de CD que representa al secundario del flyback en baja frecuer                                                              | ıcia. |

| VLam           | Voltaje promedio de la lámpara.                                                                                                               |       |

| vr             | Voltaje instantáneo rectificado.                                                                                                              |       |

| Vr             | Voltaje pico rectificado.                                                                                                                     |       |

# Acrónimos.

AC-DC Convertidor de Corriente Alterna a Corriente Directa

CA Corriente Alterna.

CD Corriente Directa.

CENIDET Centro Nacional de Investigación y Desarrollo Tecnológico.

FIDE Fideicomiso para el Ahorro de Energía.

FP Factor de Potencia.

HID Alta Intensidad de Descarga.

LED Diodo Emisor de Luz.

MDC Modo de Conducción Discontinua

MOSFET Transistor de Efecto de Campo de Metal Oxido Semiconductor.

SEPIC Single-Ended Primary-Inductor Converter.

THDi Distorsión Armónica Total en Corriente.

VDC Voltaje de Corriente Directa.

# Capítulo 1. Introducción

#### 1.1 Antecedentes.

Un sistema de iluminación está conformado por 2 partes elementales, la Fuente de Iluminación FI y la Fuente de Alimentación FA. En cuanto a la FI, el uso del Diodo Emisor de Luz LED ha ido en incremento principalmente por su vida útil [1], es tal que por mencionar a CREE, uno de los fabricantes más importantes de estos dispositivos reporta 90,700hrs de vida útil en algunos de sus productos [2], esto condiciona a que la FA mantenga una durabilidad cercana a la del LED.

Entre los distintos elementos activos y pasivos que conforman una FA, en la literatura se reporta que los capacitores electrolíticos fallan mucho antes que cualquier otro elemento [3], esto se debe a que la vida útil de este tipo de capacitor suele ser en promedio de 10,000hrs, que comparada con la de los LEDs se convierte en un gran inconveniente para una FA.

Como solución al problema del capacitor electrolítico, en artículos recientes [4-6] y en una tesis desarrollada en el CENIDET [7], hacen uso de capacitores fabricados con material poliéster o polipropileno, este último suele tener un tiempo de vida útil mayor a 100,000hrs [8]. Sin embargo el costo de los capacitores de polipropileno disponibles en el mercado es bastante considerable comparando con los de tipo electrolítico, sí el costo es proporcional a la capacitancia, entonces se procura manejar valores de capacitancias lo más bajas posible.

Existe otro problema además del tiempo de vida útil de una FA, y es el cumplimiento de las normas en cuanto a la calidad de la energía, contenido armónico en corriente *THDi* y factor de potencia *FP* [9, 10].

De la literatura consultada es común encontrar modificaciones de topologías SEPIC y flyback, ya que al ser topologías que corrigen el *FP* de manera natural se evitan etapas adicionales para dicho propósito. La topología SEPIC no es muy recomendable explorar ya que utiliza 2 capacitores y al ser de polipropileno puede encarecer la FA; por otro lado la topología flyback utiliza un capacitor y maneja menos elementos que un SEPIC por lo que se justifica explorar otras opciones de configuración del flyback.

En la literatura se encontraron 2 artículos además de una tesis desarrollada en el CENIDET que trabajaron con variaciones del convertidor flyback, para alimentar lámparas de Alta Intensidad de Descarga HID [11] y fluorescentes [12, 13]. Dichas variaciones consiste en hacer un reacomodo estratégico del primario y secundario del flyback, se pierde el aislamiento pero se consigue reducir en un porcentaje la potencia procesada por el flyback lo que beneficia a obtener una mayor eficiencia, y lo más importante, cumplir las normas.

Cabe mencionar que ya se han trabajado otras alternativas como es el caso del convertidor resonante con filtro clase E [14] en el que hacen uso del inductor como filtro para reducir el tamaño del capacitor, es un hecho que el tiempo de vida útil de un inductor es mucho mayor al

de cualquier tipo de capacitor [3], pero el manejar grandes inductancias afecta en la eficiencia global de una FA.

#### 1.2 Planteamiento del problema.

Para el diseño de una fuente de alimentación para alimentar LEDs es necesario satisfacer 2 condiciones muy importantes, durabilidad y cumplimiento de la normas de calidad de energía, esto en una topología que utilice el menor número de elementos electrónicos.

Respecto a durabilidad ya existe una solución y es el uso de capacitores de polipropileno, sin embargo el problema radica en el costo de estos elementos que es mayor con respecto a los electrolíticos, por lo tanto la FA debe utilizar capacitores de un valor de capacitancia lo más bajo posible.

Por otro lado, el tema de cumplimiento de las normas está asociado con la corrección del factor de potencia y se busca que el proceso sea llevado con un menor número de etapas. El convertidor flyback no aislado ha sido estudiado en la literatura como una estrategia para corregir el factor de potencia en una etapa para aplicaciones de iluminación HID y fluorescentes, se reporta el cumplimiento de la norma IEC61000-3-2 clase C sin problema alguno [11-13].

La idea de utilizar el convertidor flyback no aislado como solución al problema del cumplimiento de las normas para aplicaciones LED es factible porque además de corregir el factor de potencia en una etapa, sólo utiliza un capacitor para el proceso de filtrado, esto daría resultado a una topología que cumple con los requerimientos para LEDs con un menor número de elementos electrónicos.

#### 1.3 Estado del Arte.

En la Tabla 1.1 se hace resumen de las referencias analizadas de topologías para alimentar LEDs.

| Referencias | Fecha de<br>publicación | Topología                                       | Potencia<br>del LED | Capacitancia<br>utilizada            | Eficiencia promedio | FP    | Tipo de capacitor                   |

|-------------|-------------------------|-------------------------------------------------|---------------------|--------------------------------------|---------------------|-------|-------------------------------------|

| [4]         | 2015                    | Derivación de flyback en cascada.               | 9.8W                | 4.7uF                                | 86.7%               | 97    | Polipropileno.                      |

| [7]         | 2014                    | Buck-Boost<br>seguido de un<br>convertidor Buck | 11 W                | 8.2uF                                | 88%                 | 90%   | Poliéster<br>metalizado             |

| [14]        | 2013                    | Resonante con<br>Filtro clase E.                | 30W                 | 6.8nF                                | 54%                 | 99.9% | Poliéster<br>metalizado             |

| [6]         | 2012                    | SEPIC con<br>derivación Valley<br>Fill.         | 50W                 | 2 de 22uF + 4<br>de 10uF             | 93%                 | 97.5% | Polipropileno y cerámicos multicapa |

| [5]         | 2013                    | Half Bridge.                                    | 160W                | 3 de 10uF + 2<br>de 150nF y<br>100nF | 93%                 | -     | Polipropileno                       |

Tabla 1.1. Comparativa de topologías consultadas en la literatura.

De la Tabla 1.1 se complica hacer una comparación por los distintos niveles de potencia; por similitud y fecha de publicación se consideró [4] y [7] como referencia para comparar en el apartado de resultados con respecto a la topología implementada.

A continuación se presentan las estrategias seguidas para el reacomodo del primario y secundario del convertidor flyback no aislado para aplicaciones de iluminación HID y fluorescente. Las topologías fueron analizadas mediante el APBF.

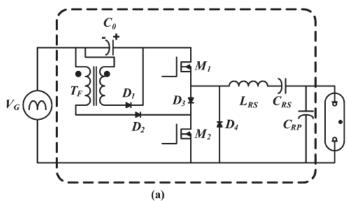

En la Figura 1.1 se muestra la topología presentada por [11], se observa que el secundario está conectado en serie con el inversor medio puente y estos en serie con el primario. Con esta configuración obtuvieron en pruebas experimentales una eficiencia del 95% y un FP=97.7% que cumple sin problema la norma IEC61000-3-2 clase C.

Figura 1.1. Flyback reacomodado para aplicaciones de iluminación HID.

En la Figura 1.2 se muestra la topología presentada por [12], se observa que el secundario está conectado en serie con el inversor medio puente y estos en paralelo con el primario. Con esta configuración obtuvieron en pruebas experimentales una eficiencia del 93% y un FP=99% que cumple sin problema la norma IEC61000-3-2 clase C.

Figura 1.2. Flyback reacomodado para aplicaciones de iluminación fluorescente.

#### 1.4 Propuesta Solución.

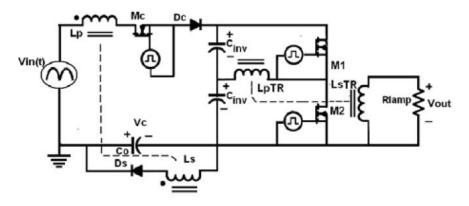

En la Figura 1.3 se muestra la topología propuesta, la variación del flyback consiste en conectar la etapa del secundario en paralelo con la lámpara LED y estas a su vez en serie con la etapa del primario.

Figura 1.3. Topología propuesta.

#### 1.5 Hipótesis.

De un convertidor flyback básico, se puede hacer un reacomodo del primario y secundario para alimentar LEDs y obtener beneficios como son mayor eficiencia de la topología y cumplimiento de las normas que si se utilizara el flyback convencional.

# 1.6 Objetivos.

# Objetivo General.

Evaluación de un convertidor flyback no aislado para aplicaciones de iluminación LED mediante el APBF.

# Objetivos específicos.

- 1. Proponer una configuración de conexión del primario y secundario de un convertidor flyback para alimentar LEDs.

- 2. Verificar si la topología cumple con las normas, y validar las ecuaciones en simulación usando PSIM.

- 3. Definir si la topología es factible de implementar en cuanto a eficiencia y el porcentaje de potencia que procesará el flyback.

- 4. Hacer el prototipo de la topología y validar los análisis matemáticos que se desarrollaron mediante pruebas experimentales.

- 5. Reporte de resultados y redacción de la tesis.

#### 1.7 Justificación.

La conexión estratégica del primario y secundario de un convertidor flyback para LEDs está justificado partiendo de los beneficios obtenidos de quienes lo hicieron para aplicaciones de iluminación HID y fluorescentes. Adicionalmente hay un aporte ya que es una topología que no está publicada en la literatura.

# Capítulo 2. Análisis de la topología propuesta

### 2.1 Modelos de trabajo para el APBF.

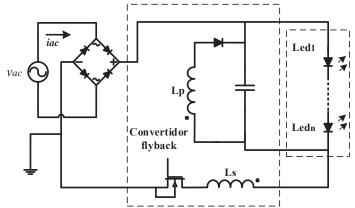

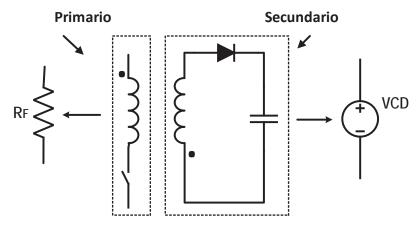

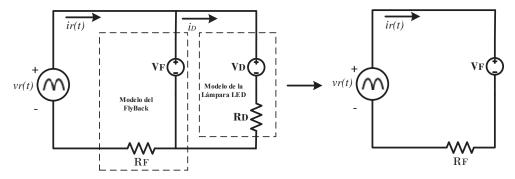

El propósito del APBF es conocer de manera general si una topología cumple con las normas, saber su eficiencia y evaluar su factibilidad de implementación. Para el caso particular del convertidor flyback Figura 2.1, el lado primario se puede visualizar como una resistencia libre de pérdidas y el secundario como una fuente de Voltaje de Corriente Directa VCD.

Figura 2.1. Modelo del flyback en MCD para el APBF.

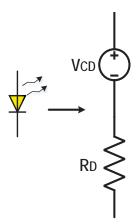

Para el LED, se puede modelar como una fuente de VCD en serie con una resistencia libre de pérdidas Figura 2.2.

Figura 2.2. Modelo del LED para el APBF.

Los modelos anteriores son indispensables para el APBF de la topología propuesta además del seguimiento de una metodología de análisis apropiada.

# 2.2 Metodología para el APBF.

En la Figura 2.3 se muestra la metodología que se desarrolló para la evaluación de la topología propuesta la cual se demostró su efectividad en resultados experimentales.

Figura 2.3. Metodología para el APBF.

Para aplicaciones de iluminación, la corriente de línea *iac* es la que se deforma con respecto al voltaje, y es la que se utiliza para medir el *FP* y el *THDi*.

De la Figura 2.3, trabajar desde un inicio con series de Fourier tiene dos propósitos:

- 1. Corroborar que la función planteada genera la misma forma de onda respecto a la que se está analizando.

- 2. Definir si la topología cumple con las normas, como referencia se tomará la IEC61000-3-2 clase C.

La relación trigonométrica de Fourier para corroborar cualquier forma de onda periódica [15], se muestra en la ecuación (1).

$$f(t) = \underbrace{a_0}_{dc} + \underbrace{\sum_{n=1}^{\infty} \left( a_n \cos\left(n\omega_0 t\right) + b_n \sin\left(n\omega_0 t\right) \right)}_{ac}$$

(1)

Donde:

La componente de "dc":

$$a_0 = \frac{1}{T} \int_0^T f(t) dt \tag{2}$$

Las componentes armónicas "ac":

$$a_n = \frac{2}{T} \int_0^T f(t) \cos(n\omega_0 t) dt \tag{3}$$

$$b_n = \frac{2}{T} \int_0^T f(t) \sin(n\omega_0 t) dt$$

(4)

$$\omega = \frac{2\pi}{T} \tag{5}$$

Sí la forma de onda a replicar es *iac*, entonces:

$$f(t) = i_{ac}(t) \tag{6}$$

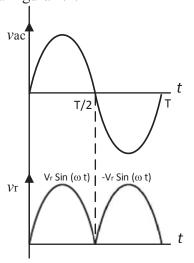

Es importante mencionar que si no hay capacitor después del puente rectificador, la forma de onda del voltaje rectificado vr es idéntica al voltaje de corriente alterna vac en medio periodo T/2, tal como se muestra en la Figura 2.4.

Figura 2.4. Formas de onda vac y vr.

Y de manera similar sucede con las formas de onda de corriente *ir* e *iac*.

Para realizar los análisis, se recomienda el uso de un programa matemático para la solución de ecuaciones, derivadas, integrales, etc., Para la solución de las diferentes expresiones matemáticas de esta tesis se utilizó MAPLE©.

#### 2.3 Evaluación de la topología.

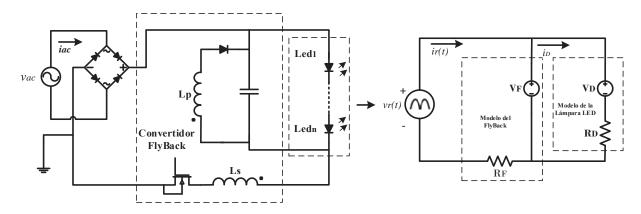

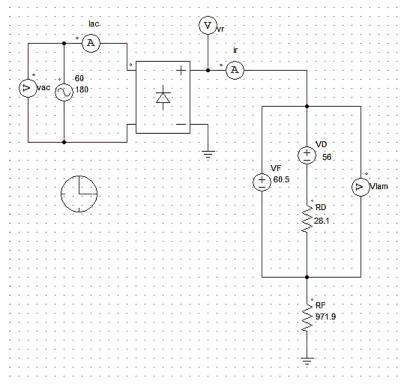

De la Figura 2.5, a la izquierda se muestra el esquemático de la topología y a lado derecho su esquema en baja frecuencia después del puente rectificador.

Figura 2.5. Esquemático de la topología propuesta y su esquema en baja frecuencia.

#### Donde:

Esquema lado derecho.

- *vr* Voltaje rectificado.

- *ir* Corriente rectificada.

- VF Fuente de voltaje VDC que representa la etapa del secundario del Flyback.

- *RF* Resistencia libre de pérdidas que representa la etapa del primario del Flyback.

- *VD* Fuente de voltaje VDC del modelo del LED.

- *RD* Resistencia del modelo del LED.

De la Figura 2.5 esquema derecho, se observa que la lámpara LED es alimentada por una fuente de C.D en este caso por VF, la equivalencia está definida con la ecuación (7).

$$V_{Lam} = V_F = V_D + i_D \cdot R_D \tag{7}$$

Como solo interesa obtener la expresión de *ir*, el esquema de la Figura 2.5 se puede ver simplificado al esquema de la Figura 2.6.

Figura 2.6. Esquema simplificado en baja frecuencia de la topología.

Aplicando ley de voltaje de Kirchhoff al esquema derecho de la Figura 2.6 se obtiene:

$$i_r(t) = \frac{v_r(t) - V_F}{R_F} \tag{8}$$

Adicionalmente del esquema de la Figura 2.6 se hacen las siguientes observaciones:

- 1. Si se desea que la topología sea reductora, entonces VF < Vr, donde Vr es la componente del voltaje pico de vr Figura 2.4.

- 2. Habrá flujo de corriente siempre y cuando VF < Vr, a medida que VF se acerque a Vr habrá tiempos muertos muy prolongados, por lo tanto, la forma de onda ir será la misma que iac en T/2 Figura 2.7.

Figura 2.7. Formas de onda de ir y de iac de la topología.

Donde tx es una constante que representa el tiempo muerto dado por la siguiente relación:

$$t_{x} = \frac{\sin^{-1}\left(\frac{V_{F}}{V_{r}}\right)}{2 \cdot \pi} = \frac{\sin^{-1}\left(m\right)}{2 \cdot \pi} \tag{9}$$

De la ecuación (9), tx es válido siempre y cuando VF < Vr.

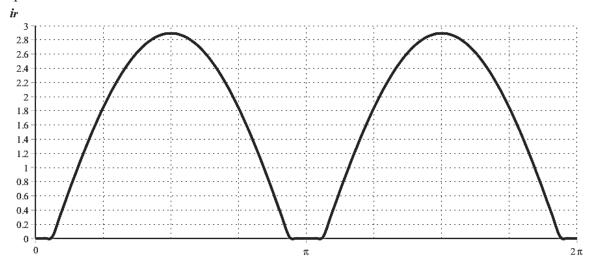

Incorporando tx en los límites de integración para calcular los coeficientes de Fourier y graficando en Maple se obtiene la forma de onda de la Figura 2.8, de la cual se observa que en efecto se obtiene la señal esperada de ir Figura 2.7. El proceso seguido en Maple se muestra en el apartado de anexos de la sección A1.

Figura 2.8. Forma de onda de ir de la topología en Maple.

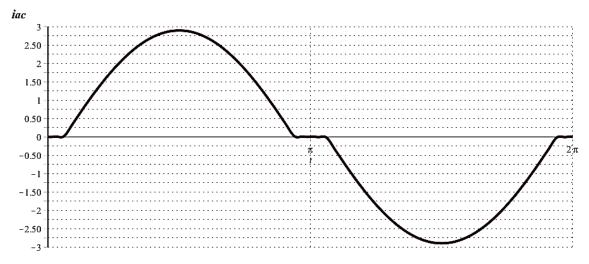

Y para la forma de onda de *iac* se muestra en la Figura 2.9, de igual manera que *ir* se observa la señal esperada de *iac*. El proceso seguido en Maple se agrega en el apartado de anexos sección A2.

Figura 2.9. Forma de onda de iac de la topología en Maple.

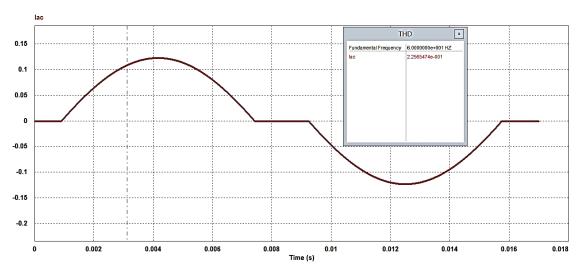

Simulando en PSIM el esquema de la Figura 2.6 se obtuvo la forma de onda de la Figura 2.10, de la cual se observa que es idéntica a la obtenida mediante series de Fourier Figura 2.9.

Figura 2.10. Forma de onda de iac de la topología en PSIM.

Habiendo comprobado que la función planteada ecuación (8) y los límites de integración utilizados en el cálculo de los coeficientes de Fourier son correctos, se prosigue a verificar si la topología cumple con requerimientos de la IEC61000-3-2 clase C.

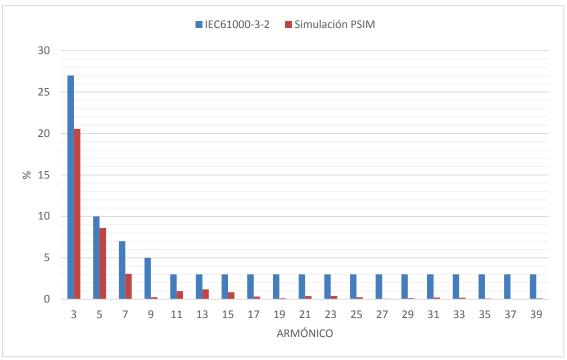

#### 2.3.1 Evaluación del contenido armónico de corriente "THDi".

Utilizando lo desarrollado en el proceso de réplica de Fourier, la forma de onda que se está analizando es una función impar, por lo tanto, solo hay armónicos impares, esto es:

Sí n=1, la componente fundamental es:

$$I_1 = 2 \cdot \cos(2 \cdot \pi \cdot t_x) \cdot \sin(2 \cdot \pi \cdot t_x) - 4 \cdot m \cdot \cos(2 \cdot \pi \cdot t_x) - 4 \cdot \pi \cdot t_x + \pi$$

(10)

La constante m es una relación del valor pico del voltaje rectificado Vr y VF, esto es:

$$m = \frac{V_F}{V_r} \tag{11}$$

Sí n=3, 5, 7,...enésimo armónico, entonces:

$$I_{n} = \frac{-4}{n \cdot (n-1) \cdot (n+1)} \cdot \sin\left(\frac{n \cdot \pi}{2}\right)^{2} \cdot \left(\frac{m \cdot (n^{2}-1) \cdot \cos(2 \cdot n \cdot t_{x} \cdot \pi) + \left(\frac{n^{2}+n}{2}\right) \cdot \sin(2 \cdot (n-1) \cdot t_{x} \cdot \pi) - \left(\frac{n^{2}-n}{2}\right) \cdot \sin(2 \cdot (n+1) \cdot t_{x} \cdot \pi)\right)$$

$$(12)$$

Finalmente el *THDi* se obtiene a partir de la siguiente relación:

$$THD_{i} = 100 \cdot \sqrt{\sum_{n=3}^{50} \left(\frac{I_{n}}{I_{1}}\right)^{2}}$$

(13)

Graficando (13) se obtiene:

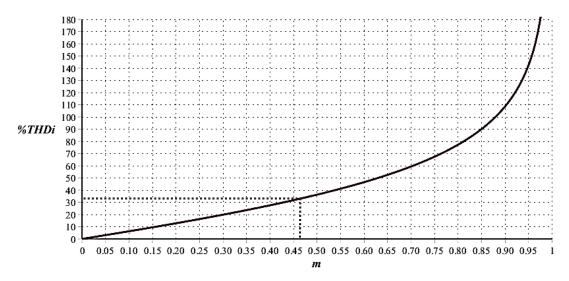

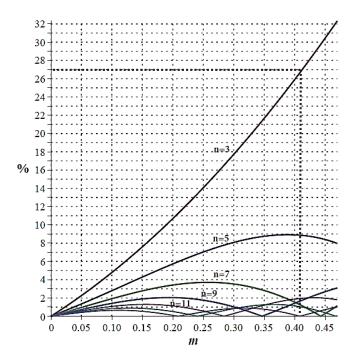

Figura 2.11. THDi de la topología.

De la Figura 2.11 se puede observar que con una m de 0 a 0.46 la topología cumple con la directivas FIDE con un  $THDi \le 32\%$ , para los requerimientos de la IEC61000-3-2 en la Figura 2.12 se muestran las curvas para los armónicos impares de n=3 a n=15, se observa que la topología está limitada en una rango de  $0 \le m \le 0.41$ .

| IEC-61000-3-2 clase C        |    |  |  |  |  |  |

|------------------------------|----|--|--|--|--|--|

| Armónico % de corriente máxi |    |  |  |  |  |  |

| 2                            | 2  |  |  |  |  |  |

| 3                            | 27 |  |  |  |  |  |

| 5                            | 10 |  |  |  |  |  |

| 7                            | 7  |  |  |  |  |  |

| 9                            | 5  |  |  |  |  |  |

| 11 a 39                      | 3  |  |  |  |  |  |

Figura 2.12. Lado izquierdo, curvas de armónicos de la topología y lado derecho requerimientos IEC-61000-3-2 clase C.

#### 2.3.2 Evaluación del factor de potencia "FP".

Retomando la ecuación (13) se obtiene el FP mediante la siguiente relación:

$$FP = \frac{1}{\sqrt{1 + \frac{THDi^2}{100^2}}}$$

(14)

Graficando la ecuación (14) se obtiene:

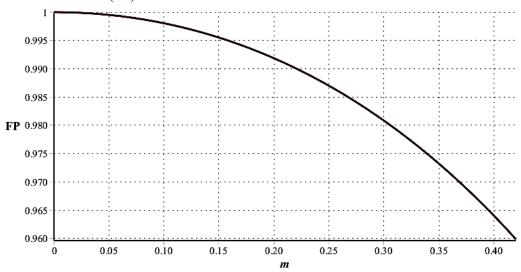

Figura 2.13. FP de la topología.

De la Figura 2.13 se observa que la topología cumple sin problema con los requerimientos de las directivas FIDE con un FP > 90 en un rango de 0 < m < 0.41.

De este apartado, la topología cumple con las normas en el rango de 0 < m < 0.41, el siguiente procedimiento es aplicar el APBF para verificar si la topología es factible de implementarse.

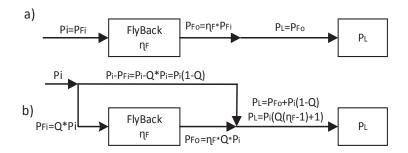

# 2.3.3 Evaluación del porcentaje de potencia procesada por el flyback "Q".

En este proceso, se designa a "Q" como una constante que representa el porcentaje de potencia que procesará el flyback, siendo esta la de mayor relevancia en un APBF. El rango de trabajo es 0 < Q < 1, sí Q es mayor a 1 no tiene caso implementar la topología, ya que en lugar de tener beneficios se obtendría todo lo contrario, baja eficiencia y mayor tamaño eléctrico con respecto a un flyback básico aislado.

Q relaciona a la potencia de entrada "lado primario "del flyback PFi y la potencia después del puente rectificador Pi:

$$Q = \frac{P_{Fi}}{P_i} \tag{15}$$

La Figura 2.14 muestra el esquema del flujo potencias de un flyback básico aislado y el de un flyback no aislado al reacomodar estratégicamente el primario y secundario.

Figura 2.14. Esquemas de flujos de potencia, a) flyback básico y b) flyback reacomodado.

Del esquema Figura 2.14, el proceso del APBF es básicamente obtener los valores promedio de voltaje, corriente o potencia según se requiera mediante la siguiente expresión.

$$f_{AVG} = \frac{1}{T} \int_{0}^{T} f(t) dt \tag{16}$$

En el apartado de anexos sección A3 se muestra el proceso para calcular Q, la expresión resultante es:

$$Q = \frac{-8 \cdot m^2 \cdot t_x \cdot \pi + 2 \cdot \pi \cdot m^2 + 2\cos(2 \cdot t_x \cdot \pi)\sin(2 \cdot t_x \cdot \pi) - 8 \cdot m \cdot \cos(2 \cdot t_x \cdot \pi) - 4 \cdot t_x \cdot \pi + \pi}{2\cos(2 \cdot t_x \cdot \pi)\sin(2 \cdot t_x \cdot \pi) - 4 \cdot m \cdot \cos(2 \cdot t_x \cdot \pi) - 4 \cdot t_x \cdot \pi + \pi}$$

(17)

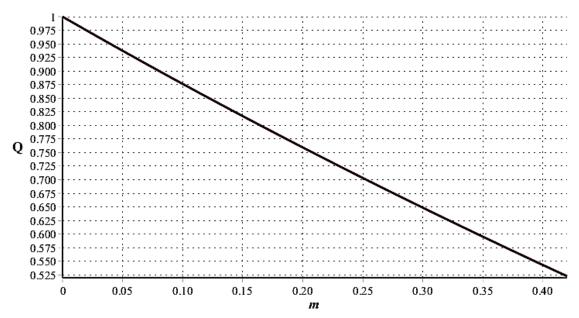

Graficando (17) se obtiene el grafico de la Figura 2.15, se observa que a medida que m crece Q disminuye, esto es bastante favorable ya que el flyback al procesar menos potencia beneficia a la eficiencia total del sistema.

Figura 2.15. Porcentaje de potencia procesada por el flyback "Q".

#### 2.3.4 Evaluación de la eficiencia total " $n_T$ ".

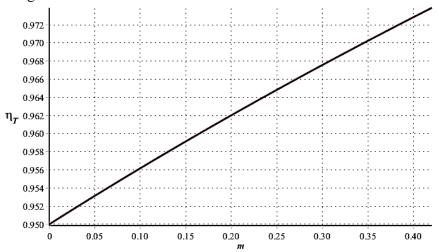

Siguiendo el esquema de la Figura 2.14 se puede obtener la eficiencia total  $n_T$  de la topología, esto es:

$$\eta_T = 1 + Q \cdot (\eta_F - 1) \tag{18}$$

Donde  $n_F$  es la eficiencia del flyback que si se propone del 95% y al sustituir en la ecuación (18) se obtiene el gráfico de la Figura 2.16, se observa que conforme m crece hay un beneficio en la eficiencia global de la topología, evidentemente si m crece hay un beneficio para Q según el gráfico de la Figura 2.15.

Figura 2.16. Eficiencia total de la topología.

Nota: Al calcular  $n_T$  no se consideran las pérdidas del puente rectificador ya que en un APFB los elementos están libres de pérdidas.

Hasta este punto se da por concluido el proceso del APBF para la topología de la cual se hacen las siguientes observaciones:

- 1. Puede cumplir con las normas en un rango de trabajo de  $0 \le m \le 0.41$ .

- 2. Tiene un comportamiento de una topología reductora siempre y cuando Vr < VF.

- 3. Se puede reducir el porcentaje de potencia procesado por el flyback "Q" en un 47%.

- 4. La topología en baja frecuencia tiene una eficiencia entre 95% y 97.5% en el rango de 0 < m < 0.41, esto es sí  $n_T = 0.95$

De lo anterior se prosigue al proceso de pruebas experimentales.

# Capítulo 3. Implementación y pruebas experimentales.

### 3.1 Cálculo de los elementos de la topología.

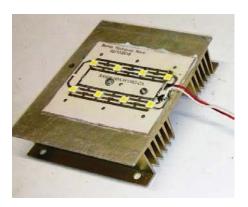

En un principio se tenía planeado utilizar alguna lámpara LED de prueba del laboratorio del Cenidet, sin embargo, con fines de comparación con las topologías [4, 7] mencionadas en la Tabla 1.1 y obtener el máximo rendimiento de la topología, se compraron LEDs del fabricante SEOUL SEMICONDUCTOR con número de parte SAW0LH0A. Se hizo un arreglo de 8 LEDs en paralelo Figura 3.1.

Figura 3.1. Lámpara LED construida con LEDs SAW0LH0A.

Las especificaciones resultantes de dicho arreglo se muestran en la Tabla 3.1, mismos que se utilizarán para simular en baja frecuencia.

Tabla 3.1. Especificaciones técnicas de la lámpara LED de prueba.

| VD  | VD RD |       | VLam  | PLam  |  |

|-----|-------|-------|-------|-------|--|

| 56V | 28.1Ω | 160mA | 60.5V | 9.68W |  |

Para el cálculo de los inductores se debe considerar el valor frontera "k" del flyback en MCD para convertidores AC-DC [16]. Con los valores de la Tabla 3.1 y las ecuaciones del anexo sección A3, se tienen los resultados de la Tabla 3.2.

Tabla 3.2. Cálculo de constantes y elementos de la topología.

| Elemento, Constante.                  | Ecuación utilizada                                       |

|---------------------------------------|----------------------------------------------------------|

| Voltaje de línea.                     | $v_{ac} = 127Vrms$                                       |

| Voltaje pico de la señal rectificada. | $V_r = 127 \cdot \sqrt{2} \approx 180V$                  |

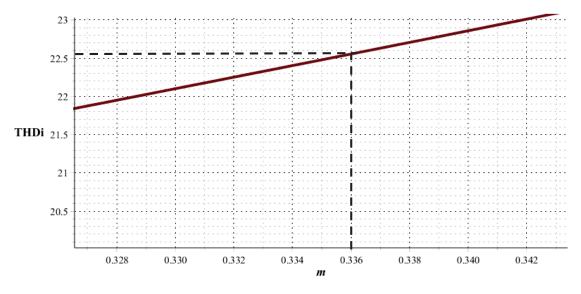

| Relación de tensiones.                | $m = \frac{V_F}{V_r} = \frac{60.5V}{180V} \approx 0.336$ |

| Tiempo muerto de <i>ir</i> .          | $t_x = \frac{\sin^{-1}(m)}{2\pi} = 54.54ms$              |

| THDi                                           | $THD_i = 22.56\% \rightarrow ecuación(27)$                                                                              |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| FP                                             | $FP = 97.55\% \rightarrow ecuación(28)$                                                                                 |

| Potencia de entrada.                           | × /                                                                                                                     |

| Impedancia del devanado Primario.              | $P_i = P_{Lam} = 9.68W$ $R_F = 971.918\Omega \rightarrow ecuación(3)$ , apartado de anexos sección A3                   |

| Potencia del devanado primario.                | $P_{Fi} = 5.904W \rightarrow ecuación(2)$ , apartado de anexos sección A3.                                              |

| Corriente rectificada promedio                 | $i_{ravg} = 62.41 mA \rightarrow ecuación(5)$ , apartado de anexos sección A3.                                          |

| Tamaño eléctrico                               | $Q = \frac{P_{Fi}}{P_i} = 60.9\%$                                                                                       |

| Eficiencia propuesta del flyback               | $\eta_{\scriptscriptstyle F} = 0.95$                                                                                    |

| Potencia promedio de<br>salida del flyback     | $P_{Fo} = \frac{Q \cdot P_i}{\eta_F} \approx 5.6W$ $V_{in} = \sqrt{P_{Fi} \cdot R_F} \approx 75.6V$                     |

| Tensión promedio en la etapa del primario.     | $V_{in} = \sqrt{P_{Fi}.R_F} \approx 75.6V$                                                                              |

| Tensión promedio en la etapa del secundario.   | $V_o = V_F = 60.5V$                                                                                                     |

| Corriente promedio en la etapa del secundario. | $I_o = \frac{P_{Fo}}{V_F} \approx 92.65 mA$                                                                             |

| Ciclo de trabajo propuesto                     | D = 0.405                                                                                                               |

| Frecuencia de conmutación trabajada.           | f = 107kHz                                                                                                              |

| Ganancia                                       | $M = \frac{V_o + V_{diodo}}{V_{in}} = \frac{60.5 + 1}{75.7} \approx 0.813$ $k = \frac{D^2}{M^2} \approx 0.248$          |

| Parámetro de<br>discontinuidad                 | $k = \frac{D^2}{M^2} \approx 0.248$                                                                                     |

| Relación de<br>transformación.                 | $N = \sqrt{\frac{1}{2 \cdot k}} - M \approx 0.607$                                                                      |

| Inductancia del primario.                      | $L_p = \frac{V_o}{I_o \cdot f \cdot (N+M)^2} \approx 757uH$                                                             |

| Inductancia del secundario.                    | $L_s = N^2 \cdot L_p \approx 278.4 uH$                                                                                  |

| Tiempo muerto del periodo de conmutación.      | $d_D = 1 - \sqrt{k} \cdot (M + N) \approx 0.293$                                                                        |

| Rizo de voltaje propuesto                      | <i>Rizo</i> = 16%                                                                                                       |

| Capacitor                                      | $C = \frac{P_i}{4 \cdot \pi \cdot 60 Hz \cdot V_F^2 \cdot Rizo} \approx 22uF \rightarrow [4]$                           |

| Capacitor EMI utilizado                        | $C_{emi} \approx 92nF$                                                                                                  |

| Inductor EMI calculado                         | $L_{emi} \approx \frac{1}{C_{emi} \cdot \left(2 \cdot \pi \cdot \frac{f}{10}\right)^2} \approx 2.7 mH \rightarrow [15]$ |

Con los valores de la Tabla 3.1 y Tabla 3.2, se prosigue a realizar el proceso de simulación y pruebas experimentales.

#### 3.2 Resultados en baja frecuencia "Ideal".

En el apartado de anexos sección A4 se muestra el circuito esquemático de la topología en baja frecuencia que se simuló en PSIM, así mismo se agregan los gráficos de las formas de onda obtenidas así como las magnitudes que se presentan en la Tabla 3.3.

|                  | THDi   | FP     | VLam   | PLam   | ID=ILam | IEC61000-3-2 |

|------------------|--------|--------|--------|--------|---------|--------------|

| Teórico.         | 22.58% | 97.55% | 60.5V  | 9.68W  | 160mA   | cumple       |

| Simulación en    | 22.56% | 97.53% | 60.49V | 9.67W  | 159.8mA | cumple       |

| baja frecuencia. |        |        |        |        |         | _            |

| % de error.      | 0.088% | 0.02%  | 0.016% | 0.103% | 0.125%  | -            |

Tabla 3.3. Resultados en baja frecuencia.

De la Tabla 3.3, los resultados son muy cercanos a los esperados, de esta forma se da validación a las ecuaciones de *THDi* y *FP*, y no solo esto, también los gráficos correspondientes son correctos, para el caso del *THDi* solo basta hacer una ampliación en Maple del gráfico de la Figura 2.11 tal como se muestra en la Figura 3.2, se observa que en efecto la magnitud de *THDi* es prácticamente exacta a la de simulación Tabla 3.3.

Figura 3.2. Gráfico ampliado de THDi de la topología.

De lo anterior, se prosigue a realizar la simulación y pruebas experimentales de topología con los elementos ya previamente calculados en la Tabla 3.2

# 3.3 Resultados en simulación y pruebas experimentales.

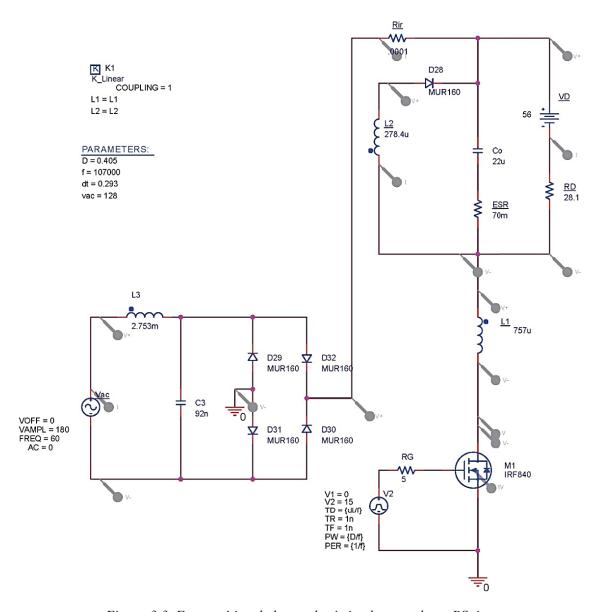

Para esta etapa se utilizó PSpice V16.6 que contienen las librerías de los semiconductores utilizados en la topología. Retomando algunos valores de la Tabla 3.1 y Tabla 3.2 se tiene el esquemático Figura 3.3 en PSpice.

Figura 3.3. Esquemático de la topología implementada en PSpice.

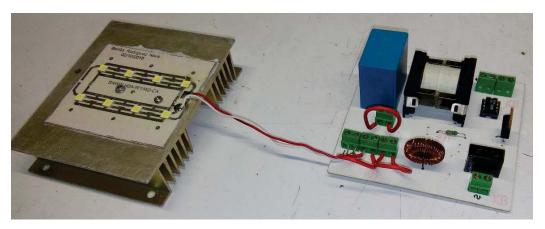

En pruebas experimentales, como impulsor del transistor Mosfet IRF840 se utilizó un drive IR2106 y con un generador de funciones se ajustó la frecuencia y el ciclo de trabajo requeridos. El prototipo para pruebas experimentales se muestra en la Figura 3.4.

Figura 3.4. Prototipo de la topología para pruebas experimentales.

Referente a los equipos de medición se utilizó un osciloscopio marca Tektronix Modelo DPO5054, y un analizador de la calidad de energía marca HIOKI modelo PW3198.

#### 3.3.1 Medición de "THDi".

En la Figura 3.5 se muestra el resultado de *THDi* generado por PSpice que es menor a 22.58% comparado con el calculado idealmente. Posteriormente se hizo la medición con el analizador de la calidad de la energía Figura 3.6, del cual se observa que el *THDi* es cercano a 22.58% y los armónicos están dentro de los requerimientos de la norma IEC61000-3-2 clase C.

```

TOTAL HARMONIC DISTORTION - 1.900974E+01 PERCENT

```

Figura 3.5. THDi obtenido en simulación PSpice.

| IEC-61000-3-2 clase C          |    |  |  |  |  |  |

|--------------------------------|----|--|--|--|--|--|

| Armónico % de corriente máximo |    |  |  |  |  |  |

| 2                              | 2  |  |  |  |  |  |

| 3                              | 27 |  |  |  |  |  |

| 5                              | 10 |  |  |  |  |  |

| 7                              | 7  |  |  |  |  |  |

| 9                              | 5  |  |  |  |  |  |

| 11 a 39                        | 3  |  |  |  |  |  |

| 1P2W 600V 50A ACD                                                                                                                                   | IME PLOT EVE<br>H<br>C 600V 500A<br>Elapsed Time<br>fFND iharmOF                                            | Udin 120V<br>fnom 60Hz<br>00:00:0 <u>0</u>                                                                                           | **<br>***********************************                                                                                   | 0                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 0: - 0.19 1: 100.00 2: 0.08 3: 19.18 4: 0.03 5: 6.29 6: 0.04 7: 3.50 8: 0.02 9: 4.68 10: 0.03 11: 2.90 12: 0.05 13: 2.98 14: 0.02 15: 2.24 16: 0.05 | 18: 0<br>19: 20: 0<br>21: 22: 0<br>23: 0<br>24: 0<br>25: 26: 0<br>27: 0<br>28: 0<br>29: 0<br>30: 0<br>32: 0 | 0.03<br>1.05<br>0.03<br>1.02<br>0.03<br>0.03<br>0.03<br>0.03<br>1.06<br>0.02<br>0.09<br>0.09<br>0.09<br>0.09<br>0.09<br>0.09<br>0.09 | \$7: 0.2<br>\$8: 0.0<br>\$9: 0.3<br>\$40: 0.0<br>\$41: 0.1<br>\$42: 0.0<br>\$43: 0.4<br>\$44: 0.0<br>\$45: 0.3<br>\$46: 0.0 | - VOLT/CURR VOLTAGE CURRENT CURRENT CURRENT HARMONICS VECTOR GRAPH LIST DMM POWER POWER VOLTAGE CURRENT CURRENT CURRENT |

| • <b>D</b> ≹ VECTOR                                                                                                                                 | GRAPH                                                                                                       | LIST                                                                                                                                 | HOLD                                                                                                                        | 2015/11/14<br>08:17:34                                                                                                  |

Figura 3.6. THDi obtenido en pruebas experimentales del medidor de la calidad de energía.

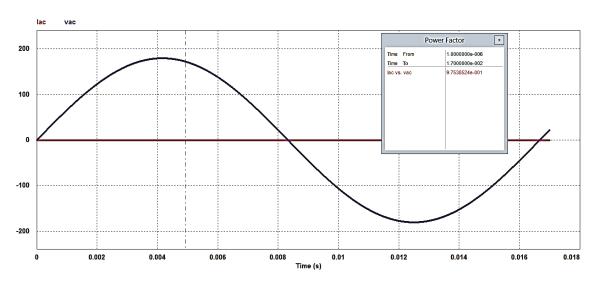

#### 3.3.2 Medición del "FP".

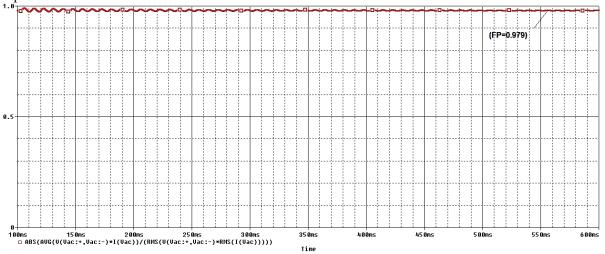

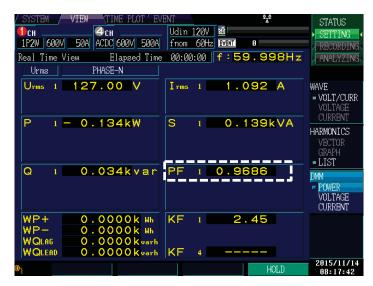

En la Figura 3.7 se muestra el gráfico del *FP* obtenido de PSpice que es aproximado al 97.55% calculado idealmente, y en la Figura 3.8 se muestra el *FP* obtenido en pruebas experimentales con el medidor de la calidad de energía, se observa que el *FP* simulación-experimental son cercanos.

Figura 3.7. FP obtenido en simulación PSpice.

Figura 3.8. FP obtenido en pruebas experimentales por el medidor de la calidad de energía.

De lo obtenido entre el *THDi* y el *FP* la topología cumple con las normas.

#### 3.3.3 Medición del voltaje en la lámpara LED.

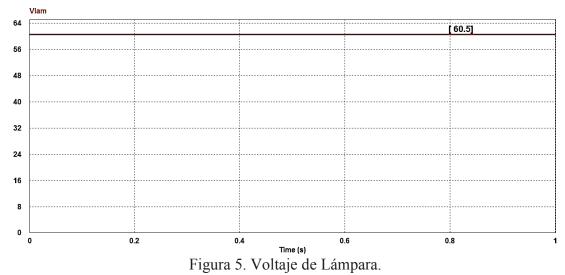

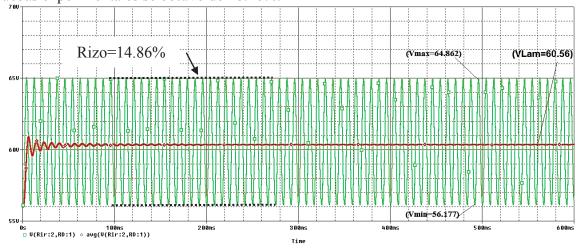

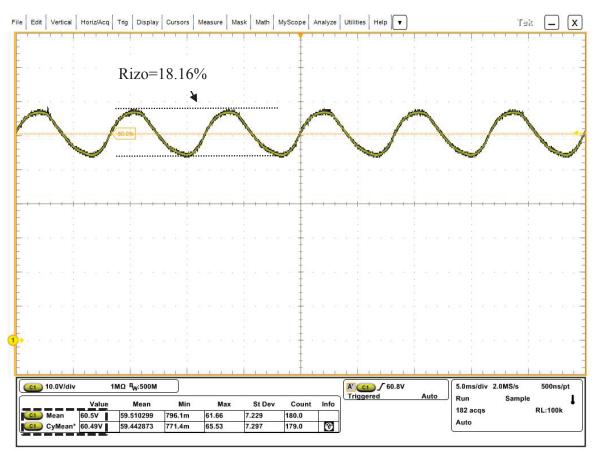

En la Figura 3.9 se muestra el voltaje instantáneo de la lámpara LED obtenido en simulación, para el caso del voltaje promedio según la Tabla 3.3 debe ser de 60.5V que es prácticamente el mismo que se obtuvo en simulación y de igual manera en pruebas experimentales Figura 3.10.

Para el rizo de voltaje, de acuerdo a la Tabla 3.2 debe ser aproximadamente del 16%, en pruebas experimentales se obtuvo de 18.16%.

Figura 3.9. Voltaje instantáneo en simulación de la lámpara LED.

Figura 3.10. Voltaje instantáneo en pruebas experimentales de la lámpara LED.

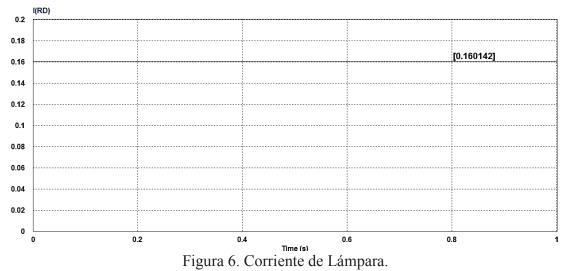

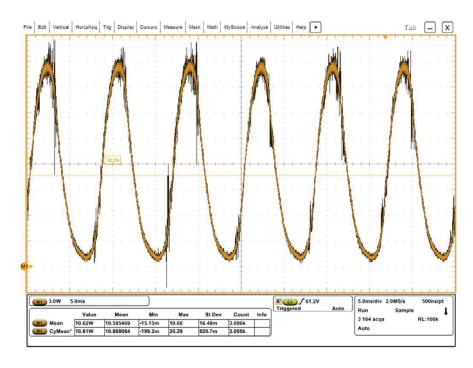

### 3.3.4 Medición de la corriente en la lámpara LED.

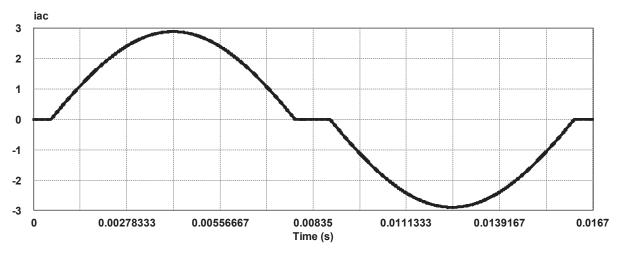

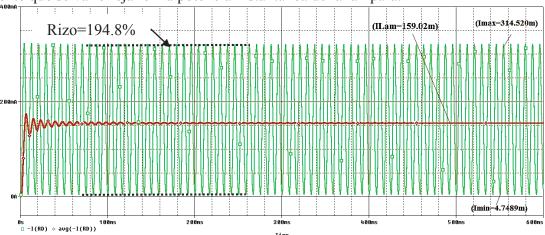

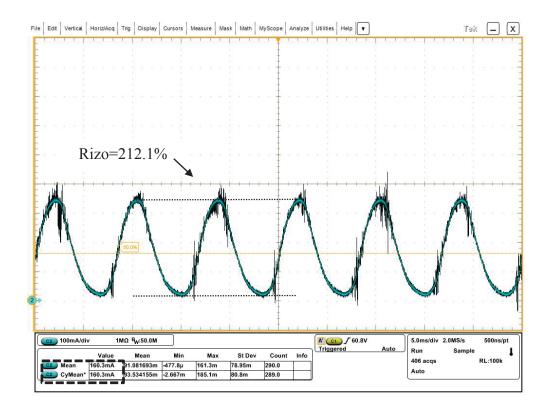

En la Figura 3.11 se muestra la corriente instantánea obtenida en simulación PSpice y en la Figura 3.12 lo obtenido en pruebas experimentales, se pude observar que los valores promedio son muy aproximados a lo esperado, sin embargo, un inconveniente es el alto rizado de corriente que se va reflejar en la potencia instantánea de la lámpara.

Figura 3.11. Corriente instantánea en simulación de la lámpara LED.

Figura 3.12. Corriente instantánea en pruebas experimentales de la lámpara LED.

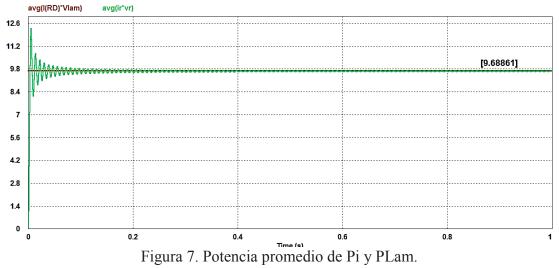

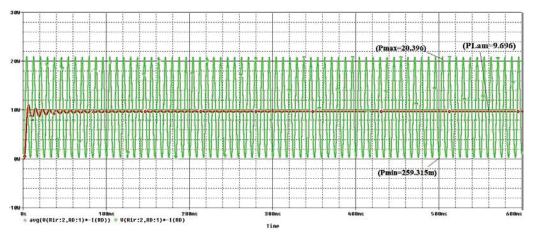

# 3.3.5 Medición de la potencia consumida por la lámpara LED.

En la Figura 3.13 se muestra la potencia instantánea obtenida en simulación y en la Figura 3.14 lo obtenido en pruebas experimentales. La potencia promedio es cercana a la esperada, sin embargo, el alto rizado de corriente se refleja en la potencia instantánea que se entrega a la lámpara LED.

Figura 3.13. Potencia instantánea en simulación de la lámpara LED.

Figura 3.14. Potencia instantánea en pruebas experimentales de la lámpara LED.

# 3.3.6 Resumen y porcentajes de error de implementación de la topología.

Finalmente en la Tabla 3.4 se hace un resumen de lo obtenido en la implementación de la topología, y como era de esperarse hay parámetros como en el caso del *THDi* que hay mayor porcentaje de error, esto se debe a que no se consideraron pérdidas de los elementos utilizados, sumado a esto la construcción del prototipo, por mencionar el transformador el cual si no está bien diseñado y embobinado puede afectar considerablemente en el desempeño de todo el sistema.

| Parámetro                                                          | Teórico-<br>Ideal | Simulación<br>PSpice | Pruebas<br>experimentales | % de error |              |              |  |

|--------------------------------------------------------------------|-------------------|----------------------|---------------------------|------------|--------------|--------------|--|

|                                                                    | Iucai             | 1 Spice              | experimentales            | Teórico-   | Teórico-     | Simulación-  |  |

|                                                                    |                   |                      |                           | Simulación | Experimental | Experimental |  |

| THDi                                                               | 22.58%            | 19%                  | 21.7%                     | -15.85     | -3.89        | 14.21        |  |

| FP                                                                 | 97.55%            | 97.9%                | 96.56%                    | 0.358      | -1.014       | -1.36        |  |

| Tensión promedio en la<br>lámpara, VLam                            | 60.5V             | 60.56V               | 60.5V                     | 0.099      | 0            | -0.099       |  |

| Rizado en VLam                                                     | 16%               | 14.86%               | 18.16%                    | -7.25      | 13.3         | 22.2         |  |

| Corriente promedio en la<br>lámpara, ILam                          | 160mA             | 159mA                | 163mA                     | -0.625     | 0.18175      | 0.8176       |  |

| Rizado en ILam                                                     | 0                 | 194.8%               | 212.1%                    | -          | -            | 8.88%        |  |

| Potencia promedio en la<br>lámpara, PLam                           | 9.68W             | 9.62W                | 10.61W                    | -0.6198    | 9.607        | 10.29        |  |

| Potencia promedio<br>rectificada Pi                                | 9.68W             | 10.4W                | 11.55W                    | 7.43       | 19.3         | 11.05        |  |

| Potencia procesada, Q                                              | 60.96%            | 61.5%                | 62.94%                    | 0.885      | 3.24         | 2.34         |  |

| Eficiencia del convertidor flyback, n <sub>F</sub>                 | 95%               | 90%                  | 88%                       | -5         | -7.36        | -2.2         |  |

| Eficiencia sin considerar el<br>puente rectificador n <sub>T</sub> | 95%               | 92.5%                | 91.4%                     | -2.63      | -3.78        | -1.189       |  |

| Eficiencia desde la línea<br>C.A a la lámpara, n <sub>S</sub>      | 95%               | 90.8%                | 88.79%                    | -4.42      | -6.53        | -2.21        |  |

Tabla 3.4. Resúmen y porcentajes de error en implementación de la topología.

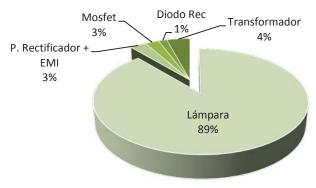

De la Tabla 3.4 se observa que independientemente de los porcentajes de error obtenidos con los dispositivos utilizados en las pruebas experimentales se obtuvo una eficiencia de 88.79%, que es mayor a lo que reportan [4, 7], y se puede mejorar si se optimiza el diseño desde utilizar un mejor transistor Mosfet, diodos rectificadores etc. En la Figura 3.15 se muestra la distribución de la potencia manejada por la topología implementada.

Figura 3.15. Distribución de la potencia manejada por la topología implementada.

Adicionalmente de la Tabla 3.4 se observa que el flyback solo procesa el 63% de la potencia de entrada, con lo que finalmente se da por aceptada la hipótesis planteada en esta tesis.

# 3.3.7 Comparativa de topologías.

En la Tabla 3.5 se hace una comparativa de 2 topologías previamente mencionadas en la Tabla 1.1 con respecto a la que se desarrolló en esta tesis.

| Topología    | Potencia<br>de<br>lámpara | THDi  | FP    | Eficiencia | Rizo de<br>corriente | Capacitor<br>utilizado | Voltaje<br>del<br>capacitor | Energía<br>en el<br>capacitor |

|--------------|---------------------------|-------|-------|------------|----------------------|------------------------|-----------------------------|-------------------------------|

| [7]          | 11W                       | -     | 90%   | 88%        | 48%                  | 8.2uF                  | 250V                        | 256.25mJ                      |

| [4]          | 9.8W                      | 17%   | 97%   | 87%        | 14.1%                | 4.7uF                  | 243V                        | 138mJ                         |

| Implementada | 10.61W                    | 21.7% | 96.56 | 88.79%     | 212.1%               | 22uF                   | 66V                         | 47.9mJ                        |

*Tabla 3.5. Comparativa de topologías de la literatura y la implementada.*

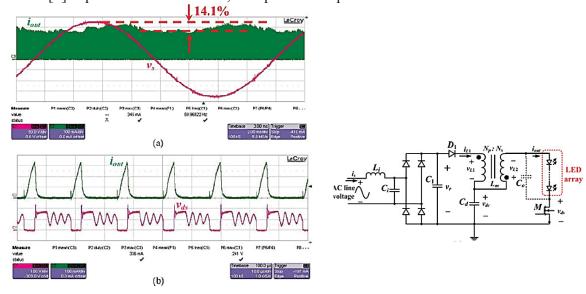

De la Tabla 3.5 la topología [4] tiene un menor porcentaje de rizo 14.1% en baja frecuencia y utiliza un valor de capacitancia bajo, sin embargo, consultando formas de onda de corriente que suministra dicha topología a una lámpara LED Figura 3.16, se observa que en alta frecuencia son pulsantes de aproximadamente 320mA, mientras que al arreglo de LED's que utilizó [4] soporta 175mA máximo, esto podría comprometer la vida útil del LED.

Fig. 22. Output LED current and MOSFET voltage (a)  $(i_{\text{out}} : 0.1 \text{ A/div}; v_{ds} : 100 \text{ V/div}; \text{time}: 10 \,\mu\text{s/div})$  (b)  $(i_{\text{out}} : 0.1 \text{ A/div}; v_s : 50 \text{ V/div}; \text{time}: 2 \,\text{ms/div})$ .

Figura 3.16. Formas de onda de corriente suministrada a una lámpara LED de la topología desarrollada por [4].

Otra observación de la topología propuesta por [4], menciona que para reducir el rizo de corriente en baja frecuencia se debe aumentar el valor del capacitor "Cd" Figura 3.16, pero en alta frecuencia el cambio sería mínimo ya que el convertidor opera en MCD, y por lo tanto, la forma de onda de corriente de los LED's seguirán siendo pulsantes, esto sencillamente porque

siguen la corriente del transistor Mosfet. En cambio, la topología desarrollada en este trabajo de tesis puede reducir el rizo de corriente con solo aumentar el valor de la capacitancia sin afectar en lo más mínimo el funcionamiento de la topología, esta opción podría comprometer en el aspecto de costos según el criterio del usuario, pero se tendría una topología que cumple con las normas en un rango 0 < m < 0.41, utiliza un menor número de dispositivos electrónicos frente a otras topologías publicadas en la literatura, y al utilizar capacitores de polipropileno la FA tendría una vida útil cercana a la del LED.

# Capítulo 4. Conclusiones y recomendaciones.

El tema de fuentes de alimentación para alimentar LEDs seguirá siendo un reto, principalmente por el capacitor de filtrado para el cual se recomienda que no sea electrolítico y que tenga un valor de capacitancia lo más bajo posible, para así incrementar la vida útil de la fuente de alimentación sin incrementar el costo.

De la hipótesis planteada en el capítulo 1 se mencionan las conclusiones de la topología.

- Da cumplimiento con los requerimientos establecidos por la norma IEC61000-3-2 clase C y las directivas FIDE en un intervalo de  $0 \le m \le 0.41$ .

- En pruebas experimentales el flyback reacomodado procesó el 63% de la potencia de entrada y el otro 37% se fue directamente a la carga, esta distribución de devanados aumenta la eficiencia de la topología, y mejora conforme el flyback procesa menos potencia.

Finalmente las ecuaciones desarrolladas se validaron mediante pruebas experimentales a una lámpara LED de 10 W, dando así por cumplido los objetivos planteados en este trabajo de tesis.

Respecto al capacitor utilizado, es menor en términos de energía comparando con [4, 14], sin embargo, el porcentaje de rizo de corriente que se entrega al LED es mayor, por lo tanto, con la topología implementada no se logró que el valor de la capacitancia se minimizará con respecto a lo que utilizan otras topologías publicadas en la literatura.

### Referente a la metodología propuesta del APBF se concluye lo siguiente:

- Contiene los elementos suficientes para aplicar el proceso del APBF a topologías parecidas a la desarrollada en esta tesis.

- Se aplicó a la topología de manera satisfactoria probando su efectividad en resultados experimentales.

### Observaciones generales.

La topología implementada en este trabajo de tesis cumple con los requerimientos para LEDs, durabilidad, cumplimientos de las normas y con un menor número de elementos electrónicos frente a topologías publicadas en la literatura, sin embargo, no se logró resolver el problema del valor del capacitor que fuera lo más bajo posible, esto resulta una desventaja de la topología en el aspecto de costos.

### Recomendaciones.

En este trabajo de tesis y por razones de tiempo solo se evaluó una de varias configuraciones posibles del convertidor flyback no aislado para aplicaciones LED, se recomienda seguir buscando otras variaciones y evaluarlas, puede que se halle una topología con mejores prestaciones que la desarrollada en esta tesis. Otra actividad pendiente fue explorar opciones de control para la topología implementada en esta tesis.

# Bibliografía

- [1] Reporte-CONUEE, "Proyecto Nacional de Eficiencia Energética en Alumbrado Público Municipal," CFE, BANOBRAS, CONUEE, México2014.

- [2] Reporte-CREE, "LED Components, IES LM-80-2008 Testing Results," USA2014.

- [3] H. M. Pang and P. M. H. Bryan, "A life prediction scheme for electrolytic capacitors in power converters without current sensor," in *Applied Power Electronics Conference and Exposition (APEC)*, 2010 Twenty-Fifth Annual IEEE, 2010, pp. 973-979.

- [4] J. C. W. Lam and P. K. Jain, "A High Power Factor, Electrolytic Capacitor-Less AC-Input LED Driver Topology With High Frequency Pulsating Output Current," *Power Electronics, IEEE Transactions on*, vol. 30, pp. 943-955, 2015.

- [5] M. Arias, D. G. Lamar, J. Sebastian, D. Balocco, and A. A. Diallo, "High-Efficiency LED Driver Without Electrolytic Capacitor for Street Lighting," *Industry Applications, IEEE Transactions on*, vol. 49, pp. 127-137, 2013.

- [6] M. Hongbo, L. Jih-Sheng, F. Quanyuan, Y. Wensong, Z. Cong, and Z. Zheng, "A Novel Valley-Fill SEPIC-Derived Power Supply Without Electrolytic Capacitor for LED Lighting Application," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 3057-3071, 2012.

- [7] J. D. Constantino-Bernal, "Análisis de Alternativas de Fuentes de Alimentación sin Capacitor Electrolítico para Lámparas de LEDs," MAESTRÍA EN CIENCIAS, Ingeniería Electrónica, CENIDET, Cuernavaca, Morelos, México, 2014.

- [8] Catálogo-EPCOS, "Metallized Polypropylene Film Capacitors (MKP)," ed, 2014, p. 36.

- [9] FIDE, "Especificación sello FIDE, Luminarios y Lamparas Integradas con Leds de uso Interior.," ed, 2014, p. 9.

- [10] M. N. Zainal-Abidin, "IEC 61000-3-2 Harmonics Standards Overview", USA2006.

- [11] M. Ponce-Silva, D. B. Luna, and M. A. Juarez, "Integrated square waveform electronic ballast with high efficiency and high power factor for high pressure sodium lamps," in *Power Electronics Specialists Conference*, 2008. PESC 2008. IEEE, 2008, pp. 2851-2856.

- [12] M. Ponce, A. J. Martinez, J. Correa, M. Cotorogea, and J. Arau, "High-efficient integrated electronic ballast for compact fluorescent lamps," *Power Electronics, IEEE Transactions on*, vol. 21, pp. 532-542, 2006.

- [13] M. d. C. Juárez-Martínez, "Diseño y Contrucción de un Balastro Electrónico de Ondas Cuadradas para Lámparas Fluorescentes," Maestría, Electrónica de Potencia, CENIDET, Cuernavaca, Morelos, 2011.

- [14] J. A. Holguín-López, "Fuente de Alimentación Resonante con un Rectificador Clase E para una Lámpara LED con Alto Factor de Potencia sin el uso de Capacitores

- Electrolíticos"," Maestría, Electronica de Potencia, CENIDET, Cuernavaca, Morelos, Edo. México, 2013.

- [15] C. K. Alexander, M. N. Sadiku, A. V. Bermúdez, and C. R. C. Pedraza, *Fundamentos de circuitos eléctricos*: McGraw-Hill, 2006.

- [16] J. Sebastian, J. A. Cobos, P. Gil, and J. Uceda, "The determination of the boundaries between continuous and discontinuous conduction modes in PWM DC-to-DC converters used as power factor preregulators," in *Power Electronics Specialists Conference*, 1992. PESC '92 Record., 23rd Annual IEEE, 1992, pp. 1061-1070 vol.2.

# Anexos

# Sección A1

# Ecuaciones en Maple del proceso de replica de ir.

# Sección A2

# Ecuaciones en Maple del proceso de replica de iac.

# Ecuaciones en Maple del APBF.

# Resultados en baja frecuencia bajo condiciones ideales de la topología en simulación PSIM.

Figura 1. Esquemático de baja frecuencia.

Figura 2. Forma de onda *iac* y *THDi*.

Figura 3. Factor de Potencia.

Figura 4. Porcentaje de armónicos tomando como referencia la norma IEC61000-3-2 clase C y los obtenidos en simulación.