# Tecnológico Nacional de México

Centro Nacional de Investigación y Desarrollo Tecnológico

## Tesis de Maestría

Análisis del Rendimiento de un Motor de Inducción Trifásico

Alimentado por un Inversor Dual

presentada por Ing. Adolfo Valdez Bahena

como requisito para la obtención del grado de Maestro en Ciencias en Ingeniería Electrónica

Director de tesis **Dr. Jesus Aguayo Alquicira**

Codirector de tesis **Dra. Susana Estefany De León Aldaco**

Cuernavaca, Morelos, México. Enero de 2020.

Centro Nacional de Investigación y Desarrollo Tecnológico Departamento de Ingeniería Electrónica

"2019, Año del Caudillo del Sur, Emiliano Zapata"

Cuernavaca, Mor., No. de Oficio: Asunto: 12/diciembre/2019 DIE/260/2019

Aceptación de documentos de tesis

#### DR. GERARDO VICENTE GUERRERO RAMÍREZ SUBDIRECTOR ACADÉMICO PRESENTE

Por este conducto, los integrantes de Comité Tutorial del **C. Ing. Adolfo Valdez Bahena**, con número de control **M18CE046** de la Maestría en Ciencias en Ingeniería Electrónica, le informamos que hemos revisado el trabajo de tesis profesional titulado **"Análisis del rendimiento de un motor de inducción trifásico alimentado por un inversor dual"** y hemos encontrado que se han realizado todas las correcciones y observaciones que se le indicaron, por lo que hemos acordado aceptar el documento de tesis y le solicitamos la autorización de impresión definitiva.

DIRECTOR DE TESIS

Dr. Jesús Aguayo Alguicira Doctor en Ciencias en Ingeniería Electrónica Cédula profesional 4706315

REVISOR 1

Doctor en Ciencias en Ingeniería Electrónica

Dr. Carlos Aguilar Castillo

Cédula profesional 3581040

**REVISOR 2**

Doctora en Ciencias en Ingeniería Electrónica

**CODIRECTORA DE TESIS**

Dr. Rodolfo Amalio Vargas Méndez

Dra. Susana Estefany de León Aldaco

Cédula profesional 10458245

Dr. Rodolfo Amalio Vargas Méndez Doctor en Ciencias en Ingeniería Electrónica Cédula profesional 9526506

M.E. Guadalupe Garrido Rivera-Jefa del Departamento de Servicios Escolares Estudiante Expediente

MPS/Irr.

C.p.

Centro Nacional de Investigación y Desarrollo Tecnológico

"2019, Año del Caudillo del Sur, Emiliano Zapata"

Cuernavaca, Morelos, 08/enero/2020

OFICIO No. SAC/003/2020

Asunto: Autorización de impresión de tesis

ING. ADOLFO VALDEZ BAHENA CANDIDATO AL GRADO DE MAESTRO EN CIENCIAS **EN INGENIERÍA ELECTRÓNICA** PRESENTE

Por este conducto, tengo el agrado de comunicarle que el Comité Tutorial asignado a su trabajo de tesis titulado "Análisis del rendimiento de un motor de inducción trifásico alimentado por un inversor dual", ha informado a esta Subdirección Académica, que están de acuerdo con el trabajo presentado. Por lo anterior, se le autoriza a que proceda con la impresión definitiva de su trabajo de tesis.

Esperando que el logro del mismo sea acorde construir aspiraciones profesionales, reciba un cordial saludo

ATENTAMENTE

Excelencia en Educación Tecnológica. "Conocimiento y tecnología al servicio de México"

SEP TecNM CENTRO NACIONAL DE INVESTIGACIÓN Y DESARROLLO TECNOLÓGICO SUBDIRECCIÓN **ACADÉMICA**

DR. GERARDO VICENTE GUERRERO RAMÍREZ SUBDIRECTOR ACADÉMICO

C.p. Departamento de Servicios Escolares. Expediente

GVGR/ego

## **Agradecimientos**

A Dios, por darme la vida y permitirme llegar hasta este momento tan importante en mi formación profesional.

A mi familia, por el apoyo incondicional y la motivación constante que me han brindado para culminar con éxito todas mis metas.

A mis directores de tesis, el Dr. Jesus Aguayo Alquicira y la Dra. Susana E. De León Aldaco, quienes con su experiencia y conocimiento me orientaron durante este trabajo de investigación.

A mis revisores, el Dr. Carlos Aguilar Castillo y el Dr. Rodolfo Amalio Vargas Méndez, por sus consejos y su valioso tiempo en la revisión de este trabajo de tesis.

A la Lic. Lorena Ruiz Ramírez, por su apoyo en los trámites de titulación y su valiosa ayuda durante mi estancia en este centro de investigación.

A mis compañeros de generación: Alan, Iván, Jahir, Joan, Jorge y Patricia, por el apoyo que me ofrecieron durante nuestra estancia en el CENIDET.

Al Centro Nacional de Investigación y Desarrollo Tecnológico (CENIDET), por darme la oportunidad de realizar mis estudios de posgrado.

Al Consejo Nacional de Ciencia y Tecnología (CONACYT), por la beca que me otorgó para poder realizar mis estudios de maestría.

### Resumen

En las últimas décadas se han propuesto diversas topologías de inversores multinivel. Entre ellas, ha ganado un gran interés la topología dual utilizada para alimentar un motor de inducción con los devanados abiertos (*Open-End Winding Induction Motor*, OEWIM por sus siglas en inglés). En particular, se destacan los beneficios en términos de la forma de onda del voltaje a la salida del inversor (con formas de onda multinivel), mayor aprovechamiento de la energía del bus de CD y mejor desempeño del motor, entre otros.

En este trabajo de tesis se presenta el diseño y construcción de un inversor dual, se describe la metodología empleada para implementar la técnica de modulación PWM en un arreglo de compuertas programables en campo (FPGA, por sus siglas en inglés Field-Programmable Gate Array) y se presenta la comparación del desempeño del inversor dual con respecto al desempeño del inversor tradicional, teniendo como carga un motor de inducción trifásico; con el fin de analizar la distorsión armónica total (THD, por sus siglas en inglés *Total Harmonic Distortion*) y la distorsión armónica total ponderada (WTHD, por sus siglas en inglés *Weighted Total Harmonic Distortion*), además, el comportamiento de parámetros relacionados con el motor, tales como: velocidad, temperatura, ruido y vibraciones.

#### **Abstract**

In recent decades, different multilevel inverters topologies have been proposed. Among them, a dual inverter fed Open-End Winding Induction Motor (OEWIM) has gained increasing interest. In particular, highlight the benefits in terms of the inverter output voltage (with stepped multilevel waveforms), improved DC bus utilization and better motor performance, among others.

This thesis project presents the design and implementation of a dual inverter, describes the methodology used to implement the PWM modulation technique in a Field-Programmable Gate Array (FPGA) and presents the comparison between the dual inverter performance and the traditional inverter performance, having as load a three-phase induction motor; in order to analyze the Total Harmonic Distortion (THD) and Weighted Total Harmonic Distortion (WTHD), as well as the behavior of the parameters related to the motor, such as: speed, temperature, noise and vibrations.

## Contenido

| Índice de figuras                                             | iv   |

|---------------------------------------------------------------|------|

| Índice de tablas                                              | vi   |

| Acrónimos                                                     | vii  |

| Nomenclatura                                                  | viii |

| Capítulo 1. Introducción                                      | 1    |

| 1.1 Antecedentes                                              | 1    |

| 1.2 Planteamiento del problema                                | 3    |

| 1.3 Objetivos                                                 | 4    |

| 1.3.1 Objetivo general                                        | 4    |

| 1.3.2 Objetivos específicos                                   | 4    |

| 1.4 Estado del arte                                           | 4    |

| 1.4.1 Motor de inducción con los devanados abiertos           | 5    |

| 1.4.2 Inversor dual para motor de inducción trifásico         | 5    |

| 1.4.3 Topologías de inversor dual reportadas en la literatura | 6    |

| 1.4.4 Conclusión de las topologías                            | 8    |

| 1.4.5 Técnica de modulación PWM                               | 9    |

| 1.5 Propuesta de solución                                     | 12   |

| 1.6 Alcances y limitaciones                                   | 13   |

| 1.7 Organización del documento                                | 13   |

| Capítulo 2. Diseño y construcción del inversor dual           | 14   |

| 2.1 Descripción general                                       | 14   |

| 2.2 Etapa digital                                             | 15   |

| 2.3 Etapa de aislamiento                                      | 16   |

| 2.4 Etapa de potencia                                         | 17   |

| 2.5 Carga                                                     | 19   |

| Capítulo 3. Implementación de la técnica de modulación        | 21   |

| 3.1 Descripción general                                       | 21   |

| 3.1.1 Dispositivos FPGA                                       | 21   |

| 3.1.2 Lenguaie VHDL                                           | 22   |

| 3.2 Técnica de modulación                                        | 23 |

|------------------------------------------------------------------|----|

| 3.3 Descripción del código                                       | 25 |

| 3.3.1 Programación en Matlab                                     | 25 |

| 3.3.2 Programación en Quartus II                                 | 26 |

| 3.3.3 Simulación en ModelSim                                     | 27 |

| Capítulo 4. Pruebas y resultados                                 | 28 |

| 4.1 Descripción general                                          | 28 |

| 4.1.1 Pruebas de la técnica de modulación                        | 28 |

| 4.1.2 Pruebas de eficiencia                                      | 32 |

| 4.1.3 Pruebas al sistema inversor – motor                        | 34 |

| 4.2 Discusión de resultados                                      | 42 |

| Capítulo 5. Conclusiones                                         | 43 |

| 5.1 Conclusiones                                                 | 43 |

| 5.2 Trabajos futuros                                             | 44 |

| Referencias                                                      | 45 |

| Anexo 1. Topologías de inversor dual reportadas en la literatura | 49 |

| Anexo 2. Diseño del PCB de la etapa de aislamiento.              | 51 |

| Anexo 3. Lista de material para la etapa de aislamiento          | 52 |

| Anexo 4. Diseño del PCB de la etapa de potencia                  | 53 |

| Anexo 5. Lista de material para la etapa de potencia             | 54 |

# Índice de figuras

| Figura | 1.1. Consumo de energia electrica en Mexico en 2012 [2]                        | . 1 |

|--------|--------------------------------------------------------------------------------|-----|

| Figura | 1.2. Inversor tradicional (2 niveles)                                          | . 2 |

| Figura | 1.3. Inversor multinivel en cascada trifásico (5 niveles)                      | . 3 |

| Figura | 1.4. Esquema de conexión I) Estrella (Y) y II) Devanados abiertos              | . 5 |

| Figura | 1.5. Inversor dual para motor de inducción trifásico                           | . 6 |

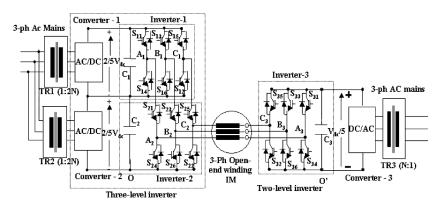

| Figura | 1.6. Topologías de inversor dual reportadas en la literatura                   | . 6 |

| Figura | 1.7. Clasificación de las variantes de la topología 1                          | . 7 |

| Figura | 1.8. Inversor dual para motor de inducción trifásico                           | . 9 |

| Figura | 1.9. Esquema del inversor dual utilizando la técnica de modulación             | . 9 |

| Figura | 1.10. Clasificación de las técnicas de modulación multinivel [6]               | 10  |

| Figura | 1.11. Principio de operación de la modulación PWM senoidal                     | 11  |

| Figura | 1.12. Señales portadoras y moduladora utilizando la modulación CBSV-PWM        | 12  |

| Figura | 1.13. Esquema representativo de la propuesta de solución                       | 13  |

| Figura | <b>2.1.</b> Etapas que integran la plataforma de pruebas                       | 14  |

|        | <b>2.2.</b> FPGA Altera Cyclone II EP2C5T144                                   |     |

| _      | <b>2.3.</b> Circuito optoacoplador para las señales PWM                        |     |

| Figura | 2.4. Esquema de conexión del módulo IRAM136-1561A                              | 18  |

| Figura | 2.5. Valor del capacitor bootstrap en función de la frecuencia de conmutación  | 19  |

| Figura | 2.6. Esquema de conexión del inversor puente completo trifásico                | 19  |

| Figura | 2.7. Esquema de interconexión entre bobinas del motor                          | 20  |

| Figura | 2.8. Plataforma de pruebas del inversor dual para motor de inducción trifásico | 20  |

| Figura | <b>3.1.</b> Arquitectura interna de un FPGA                                    | 22  |

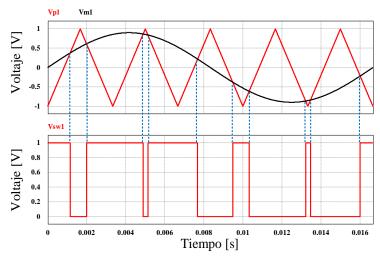

| <b>Figura 3.2.</b> Señales utilizando la modulación CBSV-PWM. I) Señales portadoras y moduladora para la fase A y II) Señales de comando para los DSeP | 25 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 3.3. Esquema del proceso empleado para generar las señales PWM                                                                                  | 26 |

| Figura 3.4. Modelo RTL del generador PWM creado en Quartus II                                                                                          | 27 |

| Figura 3.5. Señales PWM obtenidas mediante simulación en ModelSim                                                                                      | 27 |

|                                                                                                                                                        |    |

| Figura 4.1. Diagrama de conexión del inversor dual y la técnica de modulación                                                                          | 29 |

| <b>Figura 4.2.</b> Voltaje <i>V<sub>AA'</sub></i> obtenido con un desfasamiento de 180°                                                                | 30 |

| <b>Figura 4.3.</b> Voltaje <i>V<sub>AB</sub></i> obtenido con un desfasamiento de 180°                                                                 | 31 |

| <b>Figura 4.4.</b> Voltaje $V_{AA'}$ en función del ángulo de desfasamiento ( $\alpha$ )                                                               | 31 |

| Figura 4.5. Esquema de conexión para las pruebas con el inversor tradicional                                                                           | 32 |

| Figura 4.6. Esquema de conexión para las pruebas con el inversor dual                                                                                  | 33 |

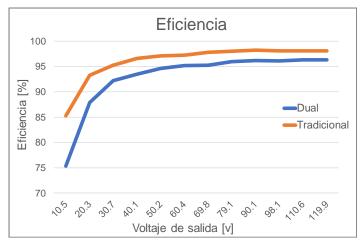

| Figura 4.7. Resultados obtenidos en las pruebas de eficiencia                                                                                          | 34 |

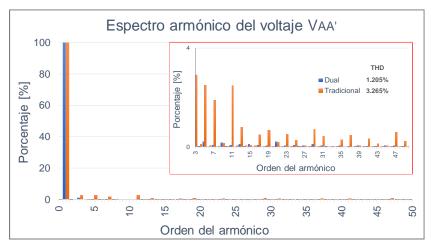

| Figura 4.8. Espectro armónico del voltaje $V_{AA'}$                                                                                                    | 36 |

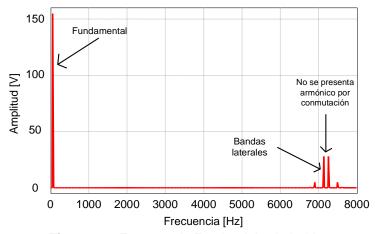

| <b>Figura 4.9.</b> Espectro de Fourier del voltaje $V_{AA'}$                                                                                           | 37 |

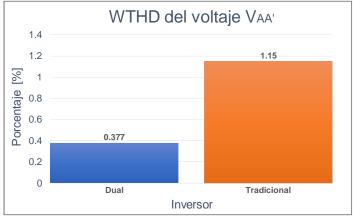

| Figura 4.10. Porcentaje de WTHD del voltaje $V_{AA'}$                                                                                                  | 37 |

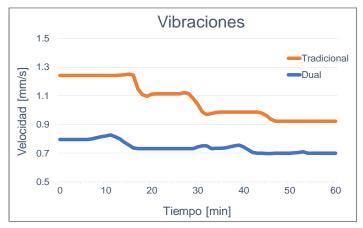

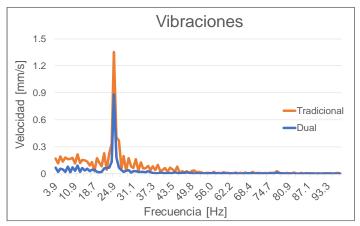

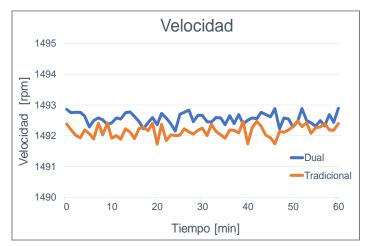

| Figura 4.11. Cambio de las vibraciones con respecto al tiempo                                                                                          | 38 |

| Figura 4.12. Espectro de vibraciones del motor                                                                                                         | 39 |

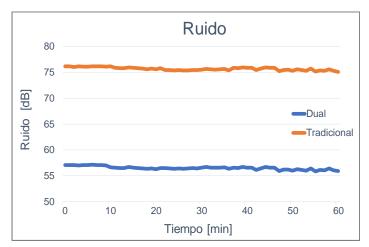

| Figura 4.13. Variación del ruido con respecto al tiempo                                                                                                | 40 |

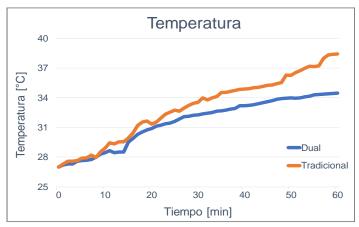

| Figura 4.14. Variación de la temperatura con respecto al tiempo                                                                                        | 41 |

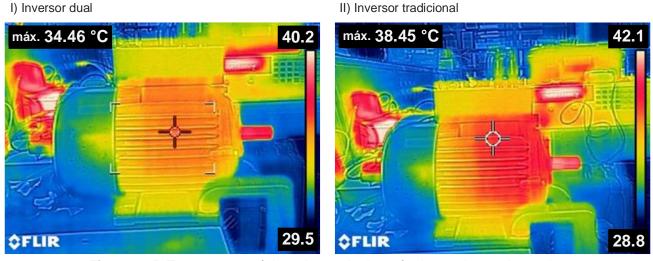

| Figura 4.15. Temperatura máxima alcanzada después de 60 minutos de prueba                                                                              | 41 |

| Figura 4.16. Variación de la velocidad con respecto al tiempo                                                                                          | 42 |

## Índice de tablas

| Tabla 1.1. Comparación de las topologías de inversor dual reportadas en la literatu | ıra 8 |

|-------------------------------------------------------------------------------------|-------|

| Tabla 2.1. Especificaciones técnicas del optoacoplador HCPL2631                     | 16    |

| Tabla 2.2. Especificaciones técnicas del módulo IRAM136-1561A                       | 17    |

| Tabla 4.1. Parámetros utilizados en simulación                                      | 29    |

| Tabla 4.2. Equipos utilizados para medir los parámetros de estudio                  | 34    |

| Tabla 4.3. Especificaciones para las pruebas al sistema inversor-motor              | 35    |

| Tabla 4.4. Límites de distorsión armónica del voltaje                               | 36    |

| Tabla 4.5. Resultados de las pruebas experimentales                                 | 42    |

## **Acrónimos**

APOD Disposición alterna opuesta de fase

CA Corriente Alterna

CBSV Modulación vectorial basada en portadora

CD Corriente Directa

CENIDET Centro Nacional de Investigación y Desarrollo Tecnológico

CMLI Inversor multinivel en cascada

DSeP Dispositivos Semiconductores de Potencia

DSP Procesador digital de señales

FPGA Arreglo de compuertas programables en campo

HDL Lenguaje de descripción de hardware

IGBT Transistor bipolar de compuerta aislada

JTAG Protocolo serie para la verificación de circuitos electrónicos

LED Diodo emisor de luz LUT Tabla de búsqueda

Matlab Programa de cálculo numérico orientado a matrices

NEMA Asociación nacional de fabricantes eléctricos

OEWIM Motor de inducción con los devanados abiertos

PCB Placa de circuito impreso

PD Disposición de fase

POD Disposición opuesta de fase

PWM Modulación por ancho de pulso

RAM Memoria de acceso aleatorio

RTL Transferencia lógica de registros

RPM Revolución por minuto

SPWM Modulación PWM senoidal

THD Distorsión armónica total

VHDL Lenguaje de descripción de hardware de alta velocidad

## Nomenclatura

Índice de modulación de amplitud ma Índice de modulación de frecuencia  $m_{\text{f}}$  $V_{m}$ Voltaje de la señal moduladora  $V_p$ Voltaje de la señal portadora Amplitud de la señal moduladora  $A_{m}$  $A_p$ Amplitud de la señal portadora Frecuencia de la señal moduladora  $f_{m}$ Frecuencia de la señal portadora fp  $S_p$ Número de señales portadoras t Tiempo  $S_c$ Número de señales portadoras Número de niveles en el voltaje de salida n Interruptor de potencia  $S_w$ Voltaje en el bus de CD  $V_{CD}$ R Resistencia Ángulo de desfasamiento α  $V_{AA}$ Voltaje de la fase A  $V_{AB}$ Voltaje de línea  $P_{e}$ Potencia de entrada  $P_s$ Potencia de salida dV/dt Incremento de voltaje por unidad de tiempo

## Capítulo 1. Introducción

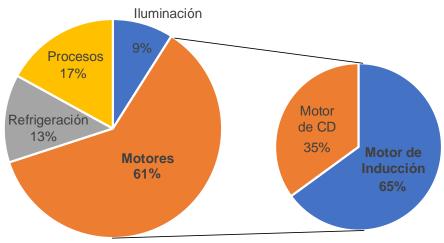

Actualmente, uno de los principales problemas que enfrenta la industria es reducir el alto nivel de consumo eléctrico. En México, el costo por la generación de energía eléctrica es de los más altos a nivel mundial. En comparación con las tarifas eléctricas de los Estados Unidos, la industria en México paga en promedio un 25% más por la energía consumida [1]. En la Figura 1.1 se muestra la distribución del consumo de energía eléctrica en la industria, el porcentaje de consumo se divide en cuatro secciones: motores, refrigeración, procesos e iluminación. Los sistemas accionados por motores eléctricos que se utilizan en procesos industriales consumen el 61% de la electricidad usada en ese sector, predominando el uso de motores de inducción con un 65%. En consecuencia, es posible reducir el consumo de energía en las industrias implementando mejoras en la eficiencia de estos motores impactando significativamente en las utilidades de las empresas y el medio ambiente [2].

#### Consumo de electricidad en la industria

Figura 1.1. Consumo de energía eléctrica en México en 2012 [2]

#### 1.1 Antecedentes

La importancia de los motores de inducción se debe a su construcción simple pero robusta, menor costo y porque proporciona un excelente servicio con muy poco mantenimiento. Sin embargo, su inconveniente más grande es la limitación para regular su velocidad, de ahí que anteriormente se prefirieran los motores de corriente continua. Afortunadamente, con ayuda de la electrónica de potencia es posible controlar su velocidad para adaptarlos a la demanda de la carga, incluso pequeños cambios en la velocidad del motor producen cambios significativos en el consumo de energía [3].

Existen diferentes métodos para controlar la velocidad de los motores de inducción tales como: cambiando el número de polos, variando el voltaje o modificando la frecuencia de alimentación. El método más usado es la combinación de los dos últimos, debido a que se tiene un mayor intervalo de control [4]. Para lograr esto se utilizan los variadores de velocidad los cuales se componen de tres etapas importantes: rectificación, filtro e inversión.

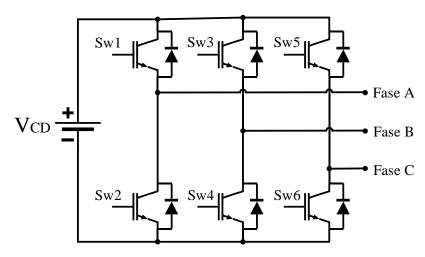

Para la etapa de inversión del voltaje se han utilizado muchas configuraciones, la más común es el inversor tradicional (ver Figura 1.2). El inversor tradicional genera únicamente dos niveles en el voltaje de salida por lo que se tienen mayores esfuerzos en los interruptores de potencia. Además, puede causar diversos problemas en el motor, tales como ruidos, vibraciones, fallas en los rodamientos, sobretensiones, entre otros. Estos inconvenientes aumentan con las altas frecuencias de conmutación a las que trabajan los Dispositivos Semiconductores de Potencia (DSeP) [4].

Figura 1.2. Inversor tradicional (2 niveles)

Una alternativa para los inversores tradicionales se encuentra en las topologías multinivel. La característica principal de los inversores multinivel es la capacidad de reducir el voltaje que deben soportar los dispositivos semiconductores de potencia, gracias a que se emplean varias fuentes de alimentación en el bus de CD. Otras ventajas que ofrecen estas topologías son: menores pérdidas por conmutación, aumento considerable en la potencia que puede soportar el inversor, mayor calidad en la señal de salida y reducción de la distorsión armónica total (THD, por sus siglas en inglés *Total Harmonic Distortion*), entre otras [4].

Por su estructura, los inversores multinivel son la mejor opción para aplicaciones de media y alta tensión, entre las topologías más utilizadas en la industria se encuentran: diodos de enclavamiento, conexión en cascada y condensadores flotantes [2].

En aplicaciones que demandan muy alta potencia (hasta 31 MW), los inversores multinivel en cascada ofrecen grandes ventajas respecto a las otras topologías, tales como:

La conexión por etapas permite tener un inversor modular, lo que facilita la sustitución de elementos ante una acción de mantenimiento.

- Requiere un menor número de componentes, con respecto a los otros inversores multinivel, para obtener el mismo número de niveles de voltaje [2, 4].

- La topología es tolerante a fallas pues, ante la falla de una etapa del inversor, los niveles del voltaje de salida se reducen sin que el inversor salga de operación.

- Capacidad de expansión en serie, debido a que, para incrementar el número de niveles en el voltaje de salida, solo es necesario conectar más inversores puente completo en cascada (obteniendo 2 niveles más por cada inversor extra).

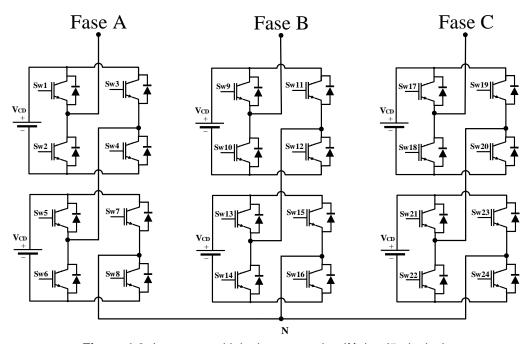

Sin embargo, al aumentar el número de niveles, se incrementa notablemente el número de componentes y el costo del inversor, las técnicas de modulación empleadas son más complejas y es necesario contar con diferentes niveles de voltaje en la entrada [4]. En la Figura 1.3, se muestra el diagrama de conexión de un inversor multinivel en cascada trifásico de cinco niveles, el cual utiliza dos inversores puente completo por fase.

Figura 1.3. Inversor multinivel en cascada trifásico (5 niveles)

## 1.2 Planteamiento del problema

Considerando que el motor de inducción trifásico es la máquina eléctrica más utilizada en el sector industrial, se requiere que su eficiencia sea elevada. Con el uso de convertidores de potencia es posible regular la velocidad de los motores de inducción, para operar el motor de forma más eficiente y reducir su consumo de energía [2].

Los inversores tradicionales de dos niveles son una alternativa vigente, sin embargo, presentan una serie de inconvenientes que provocan daños a la calidad de la energía, así como al comportamiento de los equipos eléctricos alimentados por los mismos, especialmente en aplicaciones de gran potencia.

Una alternativa para solucionar los problemas asociados con los inversores tradicionales es utilizar inversores multinivel, los cuales producen señales de voltaje casi senoidales (con mayor número de niveles), menores distorsiones en la corriente de la carga, menores dV/dt y menores niveles de interferencia electromagnética [5, 6]. Sin embargo, estos utilizan un mayor número de componentes, incrementando el volumen y el costo del inversor, además, las técnicas de modulación requeridas son más complejas [5-7].

Actualmente, el inversor dual ha ganado gran popularidad debido a que con esta topología es posible conservar la mayoría o incluso todas las ventajas de las topologías multinivel, pero utilizando un menor número de dispositivos semiconductores de potencia. Estas ventajas son fundamentales en aquellas aplicaciones donde la reducción de peso y volumen son factores críticos, como en las destinadas a los sectores de la energía, la movilidad, la industria, los servicios y el consumo.

### 1.3 Objetivos

## 1.3.1 Objetivo general

Diseñar y construir un inversor dual para alimentar un motor de inducción trifásico con los devanados abiertos y evaluar su desempeño con respecto al inversor tradicional, tomando en cuenta el comportamiento de parámetros referentes al motor.

## 1.3.2 Objetivos específicos

- 1. Identificar y definir las características que permiten obtener el mejor desempeño del inversor dual.

- 2. Definir la técnica de modulación que más ventajas presenta en la implementación con el inversor dual.

- 3. Evaluar el desempeño del inversor dual con un motor de inducción trifásico.

- 4. Comprobar si el desempeño del inversor dual es mejor con respecto al desempeño del inversor tradicional.

#### 1.4 Estado del arte

En las últimas décadas se han propuesto diversas topologías de inversores multinivel. Entre ellas, la topología dual utilizada para alimentar un motor de inducción con los devanados abiertos (*Open-End Winding Induction Motor*, OEWIM por sus siglas en inglés), ha ganado un gran interés. En particular, se destacan los beneficios en términos de la forma de onda del voltaje a la salida del inversor (menor THD), el factor de utilización (mayor aprovechamiento de la energía del bus de CD), eficiencia (menores pérdidas por conmutación) y mejor desempeño del motor (eliminación de las corrientes de modo común), entre otros. En esta sección, se presenta una revisión del estado del arte acerca de los sistemas con inversor dual para motores de inducción con devanados abiertos.

#### 1.4.1 Motor de inducción con los devanados abiertos

Actualmente, el motor de inducción trifásico conectado en estrella (conexión Y) es ampliamente utilizado en la industria. En esta configuración, cada fase se comporta como un motor monofásico y consume de 4 a 8 veces la corriente nominal durante el arranque, ya que requiere una potencia inicial muy grande para superar la estática del motor. A medida que el motor rompe la fuerza inercial (gana velocidad), la corriente disminuye hasta que alcanza la corriente nominal.

Una forma de reducir la corriente en el momento del arranque (consumo excesivo de energía), es usar un circuito de arranque de bajo voltaje. Al reducir el voltaje se reduce proporcionalmente la corriente, la intensidad del campo magnético y el par motriz. Entre los métodos de arranque a tensión reducida más utilizados se pueden citar; el arranque con autotransformador, conexión estrella-delta y con variador de frecuencia.

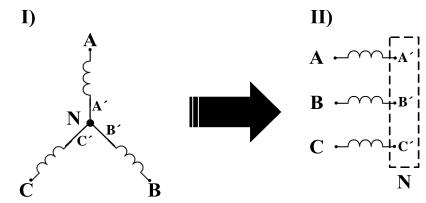

Otra propuesta interesante para reducir el voltaje en los terminales del motor, es utilizar la conexión con los devanados abiertos. Esta configuración se obtiene desconectando las terminales del punto neutro en un motor conectado en estrella (ver Figura 1.4). Con esta modificación se logra tener menores pérdidas, menor rizo del par, menos ruido y tolerancia a fallas [8]. Además, en la mayoría de los casos, no es necesario realizar ninguna modificación eléctrica o mecánica para operar la misma máquina que antes operaba en conexión delta o estrella. Debido a que la mayoría de los motores diseñados para aplicaciones de alta potencia tienen disponibles los seis terminales en la caja de conexiones, con el fin de facilitar el cambio de conexión entre la configuración delta y estrella [9].

Figura 1.4. Esquema de conexión I) Estrella (Y) y II) Devanados abiertos

#### 1.4.2 Inversor dual para motor de inducción trifásico

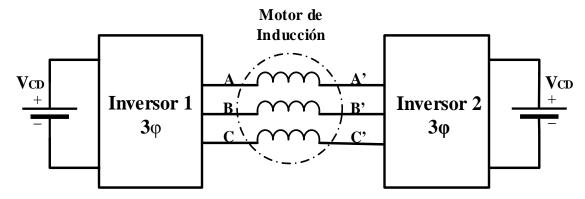

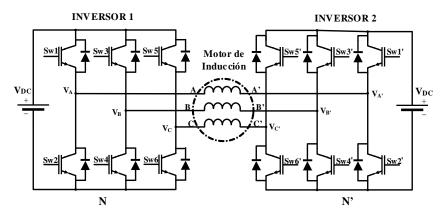

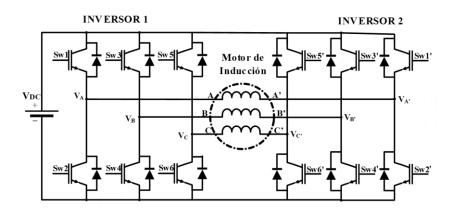

El concepto de inversor multinivel para motores de inducción con los devanados abiertos fue propuesto por H. Stemmler y P. Guggenbach en 1993. Básicamente, el término "devanados abiertos" deriva de cómo se conectan los devanados del motor a la fuente de alimentación. La idea general es alimentar ambos extremos de los devanados del estator con inversores separados, como se muestra en la Figura 1.5. Por lo tanto, el voltaje de fase queda definido por los voltajes que proporcionan ambos inversores [5].

Figura 1.5. Inversor dual para motor de inducción trifásico

El inversor dual tiene ventajas en aplicaciones donde se tienen disponibles fuentes de tensión independientes. Por ejemplo, en los vehículos eléctricos, el banco de baterías puede dividirse en dos partes para alimentar ambos inversores [6], en los vehículos híbridos, ambos inversores pueden alimentarse con dos generadores separados, por lo que no es necesario un transformador [6]; en aplicaciones fotovoltaicas conectadas a la red, los convertidores se pueden alimentar con dos arreglos fotovoltaicos separados o se puede utilizar un banco de baterías para uno de los convertidores [5, 9]. También se puede utilizar para la propulsión eléctrica de barcos, donde uno de los convertidores se conecta a un banco de capacitores y el otro suministra toda la potencia necesaria [5-7, 9].

#### 1.4.3 Topologías de inversor dual reportadas en la literatura

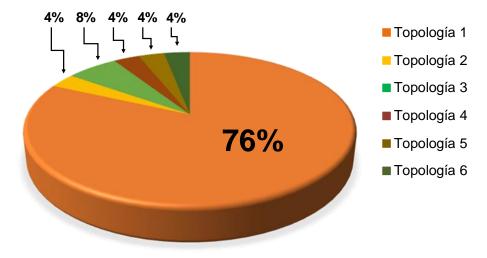

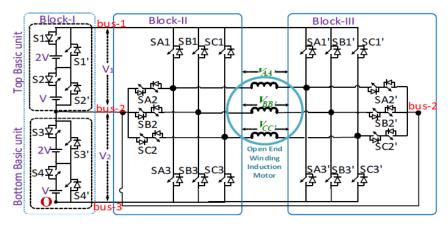

Se realizó una búsqueda en la base de datos *IEEE Xplore*, utilizando como palabras clave: *Dual inverter*, *Induction motor* y *Open-End Winding Induction Motor*. El periodo de búsqueda se acotó a 2013-2018. Se analizaron 33 artículos, identificando 6 topologías, en la Figura 1.6 se muestra el porcentaje de artículos en los que se encuentra cada topología.

Figura 1.6. Topologías de inversor dual reportadas en la literatura

El circuito eléctrico de cada topología se muestra en el Anexo 1. Para distinguir entre los distintos circuitos se les denominará Topología 1 – 6. Sin embargo, todas son inversor dual, solo cambia el tipo de inversor que alimenta cada lado del motor.

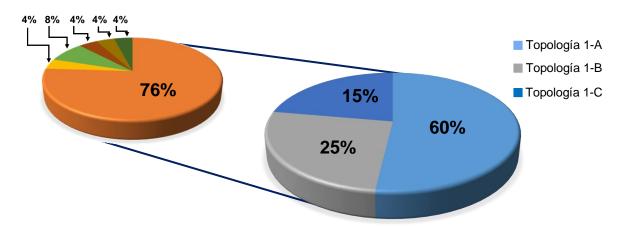

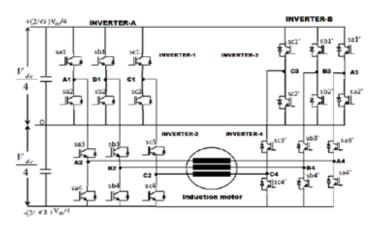

**Topología 1**. De acuerdo con la literatura consultada, se ve una clara tendencia a utilizar la topología 1, compuesta por dos inversores de 2 niveles. De esta configuración se tienen tres variantes (Figura 1.7), las cuales se explican a continuación:

Figura 1.7. Clasificación de las variantes de la topología 1

- Topología 1-A. Se utilizan dos inversores de 2 niveles, cada uno alimentado por una fuente de voltaje. Las fuentes de CD aisladas se utilizan para bloquear el flujo de corrientes armónicas y eliminar las fluctuaciones de punto neutro. La desventaja de esta configuración es que se requieren dos fuentes aisladas, las cuales normalmente se obtienen utilizando un transformador (incrementando el volumen del sistema) [16-30].

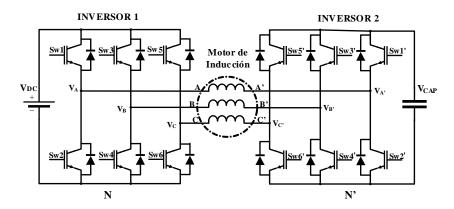

- Topología 1-B. En esta configuración se sustituye una fuente de CD por un capacitor, el cual proporciona energía reactiva al motor y compensa las caídas de voltaje. En comparación con la anterior se reduce el tamaño del inversor al requerir solo una fuente. Sin embargo, es necesario un esquema de modulación que controle la carga y descarga del capacitor, lo cual es complicado, incrementa el número de conmutaciones y reduce un 33% el factor de utilización del bus de CD [8, 31-37].

- Topología 1-C. En esta topología ambos inversores se conectan a una sola fuente de alimentación, reduciendo el tamaño del inversor. Sin embargo, es necesario utilizar un esquema de modulación específico para eliminar las corrientes de modo común, lo cual reduce el factor de utilización del bus de CD en un 15% [12, 38-43].

**Topología 2**. Se utilizan dos inversores con estructura en T conectados al mismo bus de CD. Con esta configuración es posible obtener 5, 6 o 7 niveles a la salida modificando el índice de modulación [10].

**Topología 3**. Se utilizan 2 inversores con diodos de enclavamiento de tres niveles conectados al mismo bus de CD, proporcionando un voltaje de salida de 5 niveles. Comparado con el inversor con diodos de enclavamiento de 5 niveles convencional utiliza un voltaje de alimentación menor, menos diodos y presenta tolerancia a fallas [11, 12].

**Topología 4**. En esta se utilizan dos inversores de 3 niveles (puente completo en cascada), ambos conectados al mismo bus de CD, obteniendo un voltaje de salida de 5 niveles. Aunque, es necesario un esquema de modulación para eliminar las tensiones de modo común, reduciendo el número de niveles y el factor de utilización del bus (-15%) [13].

**Topología 5**. Utiliza un inversor de 3 niveles en cascada para alimentar un lado del motor y un inversor de 2 niveles para el otro. Con esta configuración se obtienen formas de onda de 2 y hasta 6 niveles, modificando el índice de modulación. Presenta menores pérdidas por conmutación, pero son necesarias 3 fuentes de alimentación aisladas [14].

**Topología 6**. Se utiliza un inversor de 2 niveles en serie con un puente H, mientras el otro lado del motor se conecta a un inversor de 2 niveles, obteniendo un inversor de 5 niveles. Presenta tolerancia a fallas incrementando la confiabilidad del sistema, sin embargo, es necesario controlar el voltaje de cada capacitor conectado al puente H [15].

#### 1.4.4 Conclusión de las topologías

En la Tabla 1.1 se muestra una comparación de las diferentes topologías encontradas en la literatura, clasificando por medio del uso de colores (tipo semáforo) la cantidad de componentes utilizados (interruptores, diodos, fuentes y capacitores) y el factor de utilización del bus de CD. De color rojo aparecen aquellos que tienen el mayor número de componentes o un menor factor de utilización, de color verde aquellos que presentan menor número de componentes y mayor factor de utilización, y de color amarillo los que estén en un rango intermedio entre los dos anteriores. En consecuencia, el que tenga más casillas color verde es la mejor opción.

**Tabla 1.1.** Comparación de las topologías de inversor dual reportadas en la literatura

| Topología             | 1-A     | 1-B        | 1-C         | 2    | 3        | 4    | 5    | 6    |

|-----------------------|---------|------------|-------------|------|----------|------|------|------|

| Referencia            | [16-30] | [8, 31-37] | [12, 38-43] | [10] | [11, 12] | [13] | [14] | [15] |

| Interruptores         | 12      | 12         | 12          | 32   | 24       | 24   | 18   | 24   |

| Diodos                | 0       | 0          | 0           | 0    | 12       | 0    | 0    | 0    |

| Fuentes               | 2       | 1          | 1           | 4    | 1        | 2    | 3    | 2    |

| Capacitores           | 0       | 1          | 0           | 0    | 2        | 2    | 3    | 3    |

| Factor de utilización | -       | -33%       | -15%        | -    | -15%     | -15% | -    | -    |

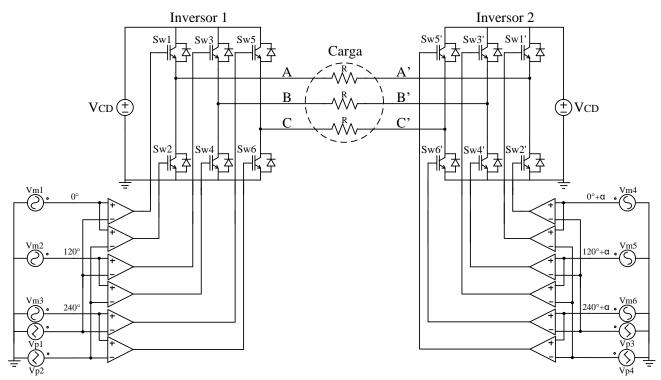

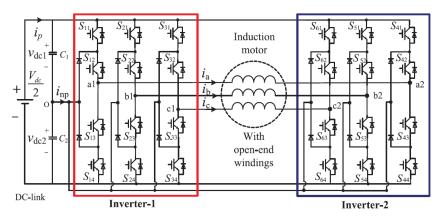

Con base en esta comparación y en el análisis de las topologías, se seleccionó la topología 1-A para la realización de este trabajo de investigación, compuesta por dos inversores puente completo trifásico alimentados con fuentes independientes, ver Figura 1.8. La característica más interesante que presenta esta topología es que, es posible obtener el mismo número de niveles que un inversor multinivel, pero utilizando un menor número de dispositivos semiconductores de potencia.

Figura 1.8. Inversor dual para motor de inducción trifásico

#### 1.4.5 Técnica de modulación PWM

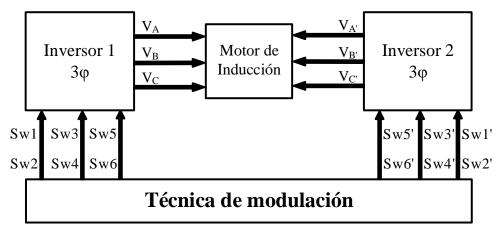

Un inversor está compuesto por un conjunto de dispositivos semiconductores de potencia con activación y desactivación controlada, como los transistores bipolares de compuerta aislada (IGBT, por sus siglas en inglés *Insulated Gate Bipolar Transistor*). La secuencia de conmutación que siguen los dispositivos IGBT viene impuesta por un proceso previo de modulación que determina las características de la señal de salida, entre ellas: forma, amplitud, frecuencia y contenido armónico [2, 3]. En la Figura 1.9 se muestra el esquema del inversor dual utilizando la técnica de modulación.

Figura 1.9. Esquema del inversor dual utilizando la técnica de modulación

Para elegir una técnica de modulación, se deben tomar en cuenta dos aspectos fundamentales: la reducción de la THD y la reducción de las pérdidas por conmutación. Una de las formas de reducir las pérdidas por conmutación es bajar la frecuencia de conmutación; sin embargo, utilizar frecuencias de conmutación bajas incrementa los armónicos de bajo orden y la THD. Al final, el propósito es tener un balance entre el nivel de armónicas, pérdidas por conmutación y frecuencia de conmutación, balance que depende de la carga a manejar mediante el inversor.

Existe una gran variedad de técnicas de modulación utilizadas en los inversores trifásicos, en la Figura 1.10 se muestra una clasificación en función de la frecuencia de conmutación. Desde el punto de vista de aplicación, en la industria se trabaja con frecuencias de conmutación muy altas, en este caso se emplean técnicas como PWM senoidal o la modulación vectorial. Para bajas frecuencias de conmutación, se utiliza la eliminación selectiva de armónicos o la modulación vectorial. La modulación de frecuencia de conmutación mixta se utiliza a menudo para convertidores híbridos [6].

Figura 1.10. Clasificación de las técnicas de modulación multinivel [6]

La técnica de modulación más utilizada es la modulación PWM senoidal (SPWM, por sus siglas en inglés *Sinusoidal Pulse Width Modulation*). Su popularidad se debe a que es fácil de implementar y a la buena distribución armónica en el espectro de la tensión de salida, el cual concentra los armónicos debidos a la conmutación en la frecuencia de la portadora y sus múltiplos (dispersándose ligeramente en las bandas laterales).

La modulación SPWM consiste en comparar una señal moduladora (senoidal) con una señal portadora (triangular), como resultado se tiene una onda cuadrada de frecuencia constante con duración de pulso variable (ver Figura 1.11). El valor eficaz del voltaje medido en los terminales de la carga depende de la relación entre la amplitud de la señal moduladora y la amplitud de la señal portadora. De esta manera se consigue controlar la cantidad de energía entregada a la carga.

Figura 1.11. Principio de operación de la modulación PWM senoidal

La señal moduladora contiene la información de amplitud, frecuencia y fase de la señal que entrega el inversor, por esta razón se le conoce también como señal de referencia [8, 9]. La señal portadora define la frecuencia de conmutación de los dispositivos semiconductores de potencia, el nivel de pérdidas por conmutación y la distorsión armónica total de la señal de voltaje a la salida del inversor [8].

Usualmente la amplitud de la señal moduladora es variable, con el fin de controlar la amplitud pico del voltaje de salida, mientras que la amplitud de la señal triangular permanece constante y lo que se modifica es su frecuencia para cambiar la frecuencia de conmutación.

Dado que utilizar una señal moduladora senoidal limita la zona lineal a un índice de modulación máximo ( $m_{max-lin} \le 1$ ) y que la utilización del bus de CD es aproximadamente un 61.2% máximo para la zona lineal y de un 78% máximo para la zona six-step. Es posible mejorar el rendimiento del inversor modificando la señal moduladora sumándole una señal de secuencia cero que, dependiendo de su composición, mejore uno de los aspectos relevantes del inversor, ya sea el aumento de la zona lineal, mayor aprovechamiento del bus de CD, menor número de conmutaciones, entre otras [44].

En la técnica de modulación con vectores espaciales basada en portadora (*Carrier Based Space Vector PWM*, CBSV-PWM por sus siglas en inglés), la señal moduladora es resultado de la suma de una señal senoidal fundamental y una señal triangular, periódica, con el triple de la frecuencia y 1/4 de amplitud de la onda senoidal fundamental. Esta técnica permite alcanzar un factor de utilización de 70.3% y presenta un buen comportamiento armónico para bajos índices de modulación, lo que la convierte en una técnica sumamente atractiva. Ofrece resultados similares a los obtenidos con la modulación vectorial con distribución simétrica de los vectores nulos [44].

Además, con el fin de reducir la distorsión armónica en el voltaje a la salida del inversor, se han desarrollado diferentes técnicas de modulación con multiportadoras, la mayoría basadas en la clásica SPWM con portadoras triangulares. Algunos métodos utilizan la disposición y otros el desplazamiento de fase de las portadoras [6].

La técnica de modulación PWM con disposición de portadoras presenta las siguientes tres variantes: disposición de fase (PD, por sus siglas en inglés *Phase Disposition*), disposición opuesta de fase (POD, por sus siglas en inglés *Phase Opposition Disposition*) y disposición alterna opuesta de fase (APOD, por sus siglas en inglés *Alternative Phase Opposite Disposition*), en las cuales únicamente varía la fase de las señales portadoras [47].

En este caso se utiliza la modulación PWM con disposición alterna opuesta de fase, en la cual las señales portadoras adyacentes se encuentran desplazadas un nivel de CD positivo o negativo y desfasadas 180° con respecto a la señal portadora adyacente [47].

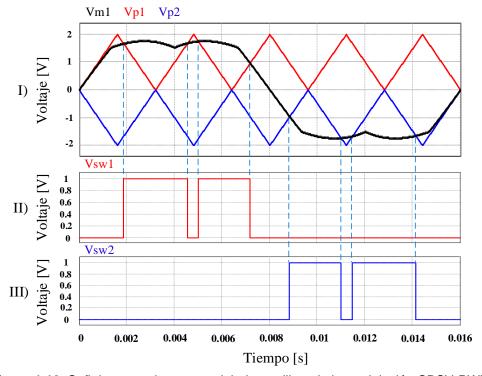

Finalmente, la técnica de modulación aplicada es una combinación de las técnicas anteriores y en lo sucesivo se le denominará simplemente CBSV-PWM. En la Figura 1.12 se muestran las señales portadoras y moduladora para la fase A, así como las señales PWM para los interruptores de potencia. Los parámetros utilizados son: m<sub>a</sub>=0.9 y m<sub>f</sub>=60.

Figura 1.12. Señales portadoras y moduladora utilizando la modulación CBSV-PWM

## 1.5 Propuesta de solución

Para garantizar un óptimo desempeño del proceso de conversión de energía y con ello prevenir pérdidas económicas para la industria, es importante estudiar el comportamiento de los inversores bajo diferentes condiciones de trabajo. De acuerdo con la literatura analizada, se observa que los parámetros que tienen mayor impacto en el proceso de conversión de corriente directa a corriente alterna son: la elección de la topología y de la técnica de modulación. Además, la mayoría de los estudios realizados se enfocan únicamente en los resultados de la THD y eliminación de las tensiones de modo común, sin tomar en cuenta el comportamiento de parámetros de la carga.

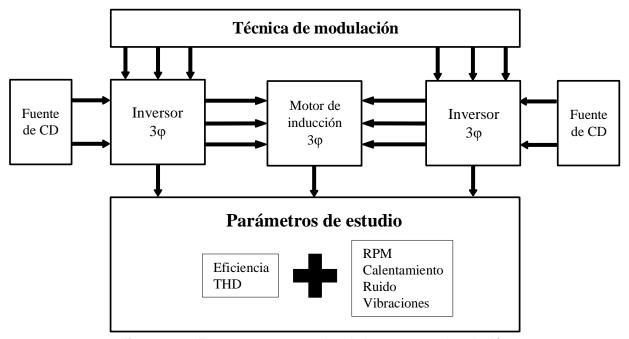

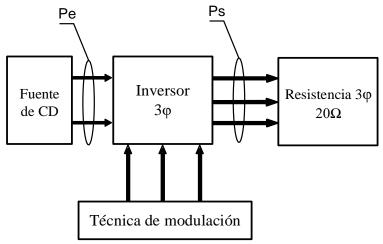

En este trabajo de tesis se propone diseñar y construir un inversor dual compuesto por dos inversores puente completo trifásico, alimentados con fuentes de CD independientes. Como carga se tiene un motor de inducción trifásico. Se propone emplear la técnica de modulación CB-SVPWM con el fin de analizar la THD, la WTHD y, además, el comportamiento de parámetros relacionados con el motor, tales como: velocidad, calentamiento, ruido y vibraciones. En la Figura 1.13 se muestra el diagrama de la propuesta solución.

Figura 1.13. Esquema representativo de la propuesta de solución

## 1.6 Alcances y limitaciones

Este trabajo de tesis tiene como alcance diseñar y construir una plataforma de pruebas que permita evaluar y comparar el desempeño del inversor dual con el desempeño del inversor tradicional teniendo como carga un motor de inducción trifásico. Las pruebas se realizaron en lazo abierto, estableciendo un punto de operación y, mediante el uso de tablas de búsqueda, se programaron dichas condiciones en una tarjeta FPGA.

#### 1.7 Organización del documento

El resto del documento está organizado de la siguiente manera: en el Capítulo 2 se explica el proceso diseño y construcción de cada una de las etapas que integran la plataforma de pruebas experimentales (para el inversor dual y el tradicional). En el Capítulo 3 se describe la metodología utilizada para implementar la técnica de modulación PWM en un dispositivo FPGA. En la Capítulo 4 se presentan las pruebas experimentales de la técnica de modulación, las pruebas de eficiencia y con el conjunto inversor – motor de inducción trifásico. Finalmente, en el Capítulo 5 se analizan los resultados obtenidos y se presentan las conclusiones del trabajo de investigación, así como los trabajos futuros.

## Capítulo 2. Diseño y construcción del inversor dual

### 2.1 Descripción general

De acuerdo con los objetivos propuestos, en este trabajo de tesis se plantea comparar el desempeño del inversor dual con respecto al desempeño del inversor tradicional. Dado que el inversor dual está compuesto por dos inversores tradicionales, el proceso de diseño se limitó a la construcción de tres inversores tradicionales con las mismas características, con el propósito de que la comparación se realicé bajo las mismas condiciones de operación. En el diseño de los inversores tradicionales se consideraron diferentes márgenes de seguridad, en cuanto a los niveles de corriente y voltaje para la selección de los dispositivos de conmutación y el capacitor del bus de CD.

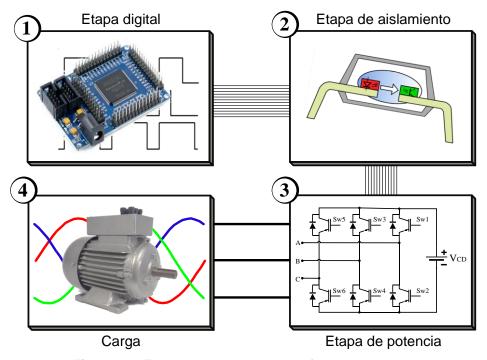

En este capítulo se describe cada una de las etapas que integran la plataforma de pruebas construida, cuyo fin es facilitar el cumplimiento de las pruebas experimentales (con el inversor dual y con el tradicional). Para el diseño de la plataforma de pruebas se consideraron cuatro actividades principales, las cuales se muestran en la Figura 2.1. A continuación, se describe cada una: 1) selección del dispositivo FPGA para la implementación de la técnica de modulación, 2) diseño y construcción de la etapa de aislamiento, 3) diseño y construcción del inversor (etapa de potencia) y 4) selección del motor de inducción trifásico.

Figura 2.1. Etapas que integran la plataforma de pruebas

#### 2.2 Etapa digital

La etapa digital consiste en una tarjeta FPGA en la cual se implementa la técnica de modulación PWM. El puerto de salida entrega 3 señales moduladas, desfasadas 120° y sus pares complementarios para cada inversor tradicional. El procedimiento empleado para generar estas señales se explica en el Capítulo 3.

Para este trabajo de tesis se seleccionó una tarjeta FPGA marca Altera® de la familia Cyclone II (ver Figura 2.2). Aunque es una tarjeta de gama baja, sus características y bajo costo la hacen una solución ideal para un gran número de aplicaciones, en especial para aquellas áreas relacionadas con el procesamiento y generación de señales. Con este FPGA es posible realizar diversos proyectos tales como: control con compuertas lógicas, máquinas de estados, procesamiento de señales serial y paralelo real, cálculos matemáticos, emulación de procesadores y más [48-51].

Figura 2.2. FPGA Altera Cyclone II EP2C5T144

Las tarjetas de la familia Cyclone II tienen un diseño compacto, y son adecuadas para la creación de prototipos como robots y proyectos "portátiles". Todos los pines de entradas/salidas están expuestos en los conectores *header* para poder usarlos con periféricos como memorias u otros módulos de expansión. El modo de programación es a través de una interfaz serie (JTAG) mediante el *ByteBlaster* de Altera. A continuación, se presentan las características principales del FPGA seleccionado:

- FPGA: Altera Cyclone II EP2C5T144.

- Voltaje de alimentación: 5 9V CD.

- Número de IO E/S: 89 de 3.3V.

- Elementos lógicos: 4608 (16 elementos lógicos por bloque).

- Bloques de memoria RAM M4K (4 Kbits + 512 bits de paridad): 26 (total: 119898 bits).

- Oscilador en la placa de 50Mhz (soporta hasta 300Mhz).

- Memoria EEPROM EPCS4 de 4Mbit en placa (programable a través del puerto ASP).

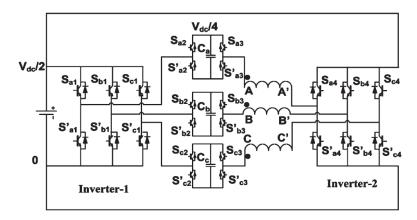

### 2.3 Etapa de aislamiento

El propósito de esta etapa, es aislar eléctricamente los dispositivos digitales (FPGA) y la etapa de potencia. Esto se logra separando el punto de referencia a tierra del FPGA y del inversor. Aislar estos dos circuitos permite proteger a la etapa digital del ruido generado por la conmutación de los transistores y minimizar el posible daño a los dispositivos de control, los cuales pueden ser costosos, a diferencia de los dispositivos de aislamiento que son económicos y accesibles.

Existen varias formas de conseguir este aislamiento entre circuitos, una de las más habituales es utilizar optoacopladores. Un optoacoplador es un dispositivo que emplea luz para conectar dos circuitos eléctricos, manteniendo un aislamiento galvánico entre ellos. El optoacoplador funciona como un interruptor activado mediante la luz emitida por un diodo *LED* que satura un componente optoelectrónico, normalmente en forma de fototransistor o fototriac. De este modo se combinan en un solo dispositivo semiconductor, un fotoemisor y un fotorreceptor cuya conexión entre ambos es óptica. Frecuentemente se incorpora una barrera dieléctrica entre emisor y receptor para aumentar el aislamiento al orden de "kV".

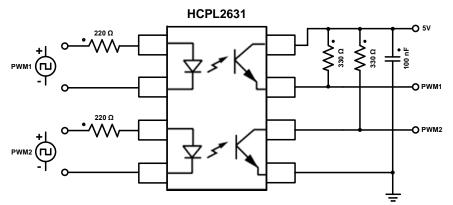

Para seleccionar el optoacoplador más adecuado es importante tomar en cuenta la frecuencia a la que conmutan los DSeP. Es recomendable que el optoacoplador tenga una frecuencia de trabajo alta, para garantizar que la señal a la salida del optoacoplador, tenga la misma forma de onda que la señal de entrada que recibe del FPGA. Con base en este criterio se seleccionó el circuito integrado HCPL2631 el cual posee un tiempo de subida y de bajada de 50 ns.

Las características principales del optoacoplador HCPL2631se muestran en la Tabla 2.1. Una de las propiedades más importantes, es que tiene una salida de puerta lógica de canal doble, lo que permite aislar dos señales con un solo integrado. También es importante mencionar que este optoacoplador invierte las señales de entrada que recibe del FPGA, es decir, recibe pulsos positivos y en la salida se obtienen pulsos negados. Es necesario considerar esta característica, con el fin de enviar las señales correctas para conmutar en la secuencia adecuada todos los dispositivos IGBT del inversor.

Tabla 2.1. Especificaciones técnicas del optoacoplador HCPL2631

| Característica                    | Valor            |

|-----------------------------------|------------------|

| Encapsulado                       | PDIP-8           |

| Velocidad de transmisión de datos | 10 Mb/s          |

| Tipo de salida                    | Colector abierto |

| Voltaje de aislamiento            | 5000 Vrms        |

| Disipación de potencia            | 60 mW            |

| Corriente de salida               | 50 mA            |

| Tiempo de caída                   | 12 ns            |

| Tiempo de subida                  | 50 ns            |

En la Figura 2.3 se muestra el esquema de conexión del circuito implementado, para aislar las señales PWM que van del FPGA al inversor puente completo trifásico, se ocuparon 3 circuitos iguales para cada inversor. En el Anexo 2 se muestra el diagrama de conexión de la placa con los tres circuitos y el diseño del PCB.

Figura 2.3. Circuito optoacoplador para las señales PWM

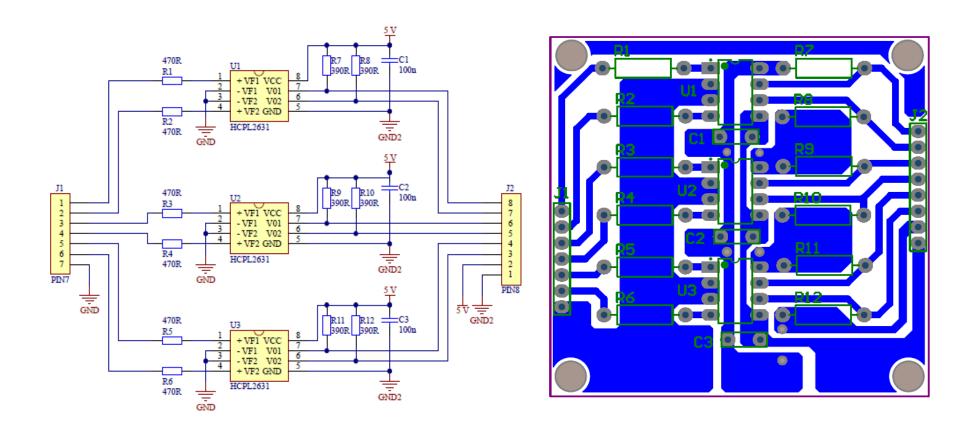

#### 2.4 Etapa de potencia

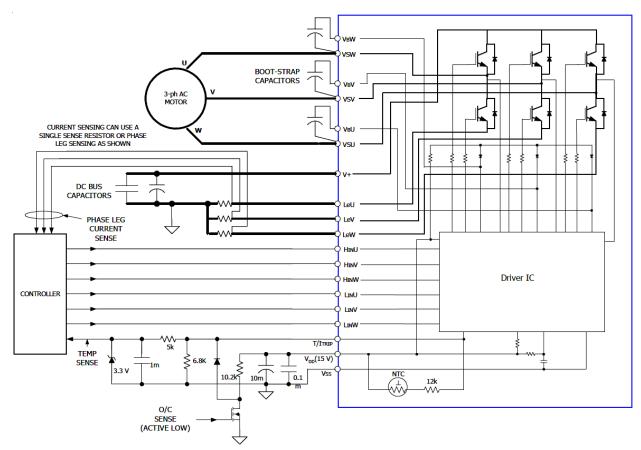

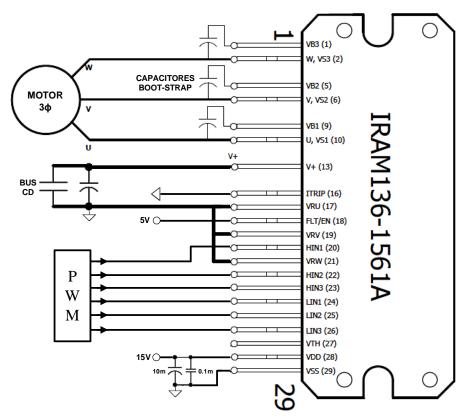

Esta etapa consiste en diseñar y construir los inversores puente completo trifásico, cuya función es convertir un voltaje de corriente directa a un voltaje de corriente alterna. Para facilitar la implementación de un circuito puente completo trifásico, es común utilizar módulos de IGBT conformados por seis dispositivos de conmutación, por ejemplo, el módulo IRAM136-1561A. Este circuito integrado está enfocado hacia aplicaciones industriales para el manejo de motores de inducción trifásicos de baja potencia. Además, tiene funcionalidades de protección y desconexión de las líneas de potencia en el caso de sobrecarga.

El módulo IRAM136-1561A se caracteriza por requerir muy pocos elementos externos para su operación. Las características principales de este módulo se presentan en la Tabla 2.2. Se puede observar que los niveles de voltaje y corriente que maneja este módulo son apropiados para alimentar motores de inducción trifásicos de hasta 1.5 kW.

| Parámetro Descripción                  |                                                   | Valor | Unidades         |

|----------------------------------------|---------------------------------------------------|-------|------------------|

| V <sub>CES</sub> / V <sub>RRM</sub>    | IGBT/ Voltaje de bloqueo del diodo FW             | 600   | V                |

| V+                                     | Voltaje positivo del bus de CD                    | 450   | V                |

| I <sub>o</sub> @ T <sub>C</sub> =25°C  | Corriente de fase RMS                             | 15    |                  |

| I <sub>o</sub> @ T <sub>C</sub> =100°C | Corriente de fase RMS                             | 7.5   | А                |

| I <sub>pk</sub>                        | Pico máximo en la corriente de fase               | 22.5  |                  |

| Fp                                     | Frecuencia de conmutación máxima                  | 20    | kHz              |

| Pd                                     | Máxima disipación de potencia por IGBT @ Tc =25°C | 32    | W                |

| Viso                                   | Voltaje de aislamiento (1min)                     | 2000  | V <sub>RMS</sub> |

| T <sub>J</sub> (IGBT & Diodo & IC)     | Temperatura de unión máxima                       | +150  | °C               |

Tabla 2.2. Especificaciones técnicas del módulo IRAM136-1561A

En la Figura 2.4 se muestra el diagrama de conexión del módulo IRAM136-1561A utilizado para el control de un motor de inducción trifásico. Los elementos que están integrados en el módulo se encuentran dentro del recuadro azul y los que se necesitan conectar de manera externa se encuentran fuera del recuadro.

Figura 2.4. Esquema de conexión del módulo IRAM136-1561A

Uno de los elementos internos con los que cuenta el módulo es un circuito que tiene la función de acondicionar las señales de mando para la activación de las compuertas de los dispositivos IGBT, por lo que no es necesario utilizar un circuito *driver* de manera externa. Además, el módulo no requiere de fuentes aisladas para conmutar los interruptores superiores de cada rama del inversor, debido a que cuenta con un modo de operación llamado *bootstrap*.

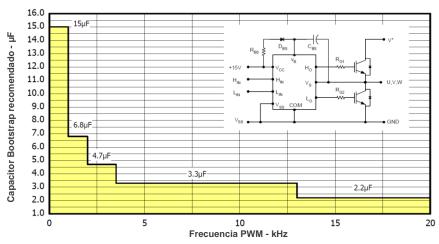

En términos generales, este modo de operación requiere de 3 diodos que están conectados de manera interna y 3 capacitores conectados de manera externa, considerando que se trata de un inversor trifásico. El valor de los capacitores depende de la frecuencia de conmutación. En la Figura 2.5 se muestra el valor recomendado del capacitor *bootstrap* en función de la frecuencia de conmutación.

Considerando una frecuencia de conmutación de 3.6 kHz el valor del capacitor *bootstrap* recomendado por el fabricante es de 3.3µF, según la hoja de datos. De acuerdo con las especificaciones de diseño propuestas por el fabricante, se utilizaron capacitores de tantalio.

Figura 2.5. Valor del capacitor bootstrap en función de la frecuencia de conmutación

Dado que, en el esquema de conexión anterior se encuentran elementos que no se requieren para el estudio que se realiza en este trabajo de tesis, el esquema empleado para el diseño del PCB de la etapa de potencia se muestra en la Figura 2.6.

Figura 2.6. Esquema de conexión del inversor puente completo trifásico

### 2.5 Carga

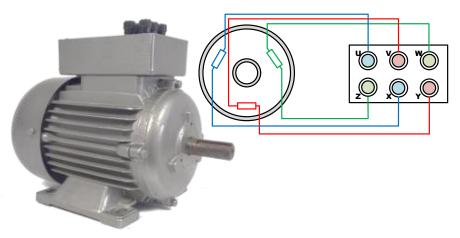

Como carga se utiliza un motor de inducción trifásico de 0.55kW marca DISTESA, modelo MR11TJX, con un voltaje nominal de trabajo de 220V/380V, y una corriente nominal de 2.6A/1.5A, su velocidad de giro es 1400RPM a una frecuencia de 60 Hz.

En la Figura 2.7 se muestra el esquema de interconexión entre bobinas del motor. Con el fin de facilitar el cambio de conexión estrella-delta, los extremos de los devanados se encuentran disponibles en una placa de conexión ubicada sobre la carcasa exterior del motor. Los bornes de dicha placa llevan la marca correspondiente a los principios (U-V-W) y finales (X-Y-Z) de los devanados. Por lo tanto, es posible realizar la conexión con devanados abiertos como lo requiere la topología dual, conectando los terminales U-V-W al inversor 1 y los terminales X-Y-Z al inversor 2, manteniendo la secuencia adecuada.

Figura 2.7. Esquema de interconexión entre bobinas del motor

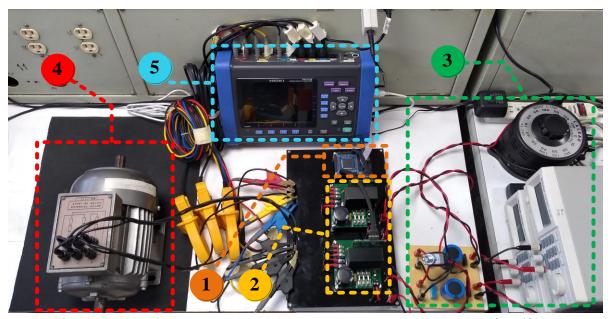

En la Figura 2.8 se muestran las distintas secciones que componen la plataforma de pruebas, en la sección 1 se encuentra el FPGA, en la sección 2 la etapa de aislamiento y el inversor dual, en la sección 3 están las fuentes de alimentación de 15V y 150V para la etapa digital y el bus de CD de cada inversor, en 4 está el motor de inducción, finalmente, en el recuadro 5 se encuentra el analizador de la calidad de la energía (*Hioki PW3198*) utilizado para medir voltajes, corrientes y la THD.

Figura 2.8. Plataforma de pruebas del inversor dual para motor de inducción trifásico

## Capítulo 3. Implementación de la técnica de modulación

### 3.1 Descripción general

El uso de técnicas de modulación PWM para inversores trifásicos se ha estudiado ampliamente [44], el método clásico de implementarlas es utilizando etapas digitales y analógicas, las cuales ocupan un espacio considerable en el área de diseño y en ocasiones son muy complicadas de implementar. Otra alternativa que se ha propuesto, es utilizar procesadores digitales de señales (DSP, por sus siglas en inglés *Digital Signal Processor*), sin embargo, en inversores multinivel donde se tienen un gran número de interruptores de potencia, se requieren dispositivos con mayor capacidad de procesamiento lo que aumenta el costo del sistema de control.

En los últimos años, se ha incrementado el uso de los dispositivos FPGA, principalmente en el desarrollo de moduladores PWM para inversores [48-51], ya que dispone de múltiples salidas, es fácil de programar, ejecuta las tareas en un tiempo reducido y, sobre todo, por su capacidad de ejecutar tareas de manera paralela [52, 54].

En este capítulo se presenta la metodología utilizada para implementar la técnica de modulación CBSV-PWM en un FPGA Altera Cyclone II. El proceso de diseño propuesto es fácil, rápido, flexible y aplicable a otras técnicas de modulación PWM.

#### 3.1.1 Dispositivos FPGA

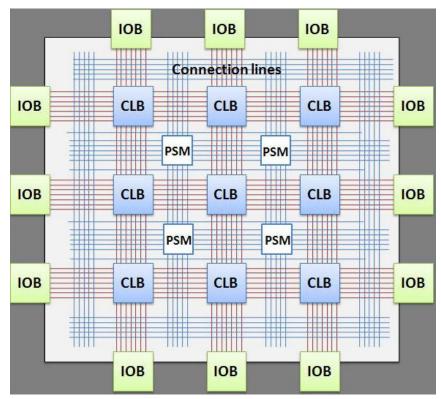

Un FPGA es un circuito integrado de electrónica digital compuesto por un arreglo matricial de bloques lógicos conectados a celdas de entrada/salida mediante canales de conexión verticales y horizontales. El FPGA tiene la capacidad de reconfigurar el hardware en su interior, ofreciendo al programador capacidades prácticamente ilimitadas para crear diseños digitales eficientes y a la medida, en comparación con un microprocesador tradicional.

En la Figura 3.1 se muestra el diagrama a bloques de la estructura básica de un FPGA. Se pueden distinguir tres bloques importantes organizados en forma de matriz: CLB (Configurable Logic Block), IOB (Input/Output Block) y PSM (Programmables Switch Matrix); estos bloques trabajan en conjunto para armar un circuito lógico dentro del FPGA y se conectan entre sí mediante las líneas de interconexión.

La capacidad del FPGA depende de la cantidad de elementos lógicos y la dimensión de la matriz. Además, dentro del FPGA se encuentra un bloque de memoria RAM embebida, que se encarga de almacenar los datos de las conexiones internas que se deben realizar para formar el circuito digital programado. Algunas tarjetas cuentan con hasta 10Mbits de memoria repartida en bloques de 36Kbits.

Figura 3.1. Arquitectura interna de un FPGA

#### 3.1.2 Lenguaje VHDL

Un FPGA no se programa de la forma tradicional, es decir, no se le graban instrucciones a seguir o ejecutar (no se crea software). Lo que se programa como código, es la descripción de un hardware que será implementado en el FPGA. Por lo tanto, lo que se desarrolla es el diseño de una arquitectura de hardware. La tarea del programador es definir la función lógica que realizará cada uno de los CLB, seleccionar el modo de trabajo de cada IOB e interconectarlos entre sí.

Para esto el diseñador cuenta con lenguajes especializados en la descripción de hardware, denominados HDL (*Hardware Description Language*). El principal objetivo de un lenguaje de descripción, es simular perfectamente el comportamiento lógico de un circuito sin que el programador necesite imponer restricciones [55]. Los lenguajes más utilizados son VHDL, Verilog y ABEL. Para este trabajo de tesis se ocupa el lenguaje VHDL, por su capacidad para el manejo de grandes proyectos logrando adaptarse a propósitos variados.

El lenguaje VHDL es sencillo, pero también muy poderoso, tiene una sintaxis amplia y flexible que permite modelar perfectamente el comportamiento de un sistema digital. Ofrece las herramientas necesarias para simular el sistema y verificar si las salidas son correctas. Esto permite crear entornos complejos de verificación para comprobar el funcionamiento del sistema, algo fundamental en diseños creados para dispositivos físicos donde un error en el diseño puede acarrear elevados costos para una empresa. Además, las descripciones de circuitos en VHDL son compatibles independientemente de la tecnología donde se va a implementar, ya que el lenguaje se convirtió en un *standard* del IEEE desde 1983.

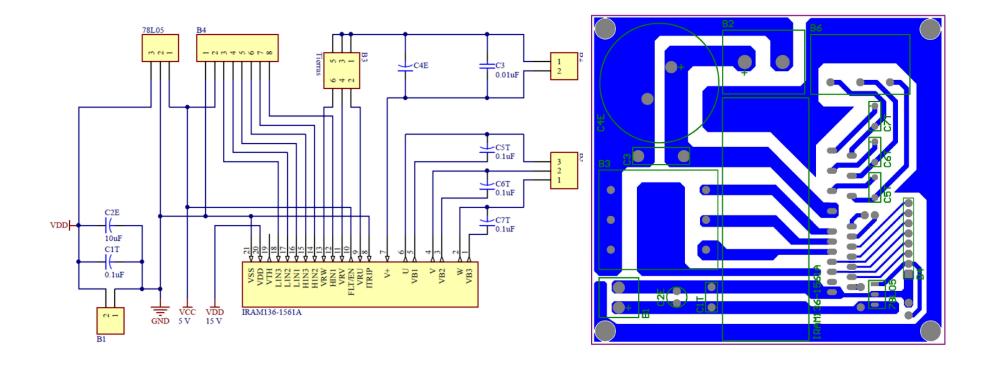

#### 3.2 Técnica de modulación

Una gran parte del desempeño de un inversor se debe a la técnica de modulación empleada para generar los estados de conmutación de los interruptores de potencia. En este sentido, se seleccionó la técnica de modulación vectorial basada en portadora (CBSV-PWM) ya que permite obtener un mayor aprovechamiento del bus de CD, y la técnica de modulación APOD-PWM, con el fin de reducir la distorsión armónica en el voltaje a la salida del inversor. En esta sección se presentan las ecuaciones utilizadas para implementar la técnica de modulación en el FPGA.

Uno de los parámetros más importantes en la modulación PWM es el índice de modulación de amplitud (m), ya que permite controlar el valor del voltaje de salida del inversor. El índice de modulación se define como la relación que existe entre la amplitud pico de la señal moduladora y la amplitud pico de la señal portadora, tal como se muestra en la ecuación (3.1). Para este parámetro se debe cumplir lo siguiente:  $0 < m_a \le 1$ , dado que un valor superior a 1 implica entrar en sobremodulación, provocando un incremento en la distorsión armónica del voltaje de salida.

$$m_a = A_{m_1} / A_{p1} (3.1)$$

Así mismo, a la relación que hay entre la frecuencia de la señal moduladora y la frecuencia de la portadora, se le denomina índice de modulación de frecuencia (m<sub>f</sub>), y se calcula con la ecuación (3.2). Para obtener un buen comportamiento armónico en el voltaje de salida, se recomienda que este índice sea mayor a 21.

$$m_f = f_{m_l} / f_{p1} {3.2}$$

Como se explicó anteriormente, en la técnica de modulación CBSV-PWM, la señal moduladora es el resultado de la suma de dos señales: una señal senoidal y una señal triangular a tres veces la frecuencia y 1/4 de la amplitud de la señal senoidal. Para generar la señal moduladora  $V_{m1}$  se utilizan las ecuaciones (3.3) y (3.4). Las señales  $V_{m2}$  y  $V_{m3}$  se encuentran desfasadas 120° y -120° respectivamente, tomando como referencia la señal moduladora  $V_{m1}$ .

$$V_m = v_x - \frac{1}{2} \left[ \max(v_x) + \min(v_x) \right]$$

(3.3)

$$v_x = A_m \sin(2\pi f_m t) \tag{3.4}$$

Dónde:

$A_m$ : Amplitud de la señal moduladora (Volts, V).

$f_m$ : Frecuencia de la señal moduladora (Hertz, Hz).

t: Tiempo (segundos, s).

Con el fin de mejorar el rendimiento armónico se utiliza una técnica con múltiples portadoras, las cuales tienen la misma amplitud con respecto a la señal moduladora de referencia. El número de señales portadoras necesarias para generar un determinado número de niveles en el voltaje de salida se calcula mediante la ecuación (3.5) [47].

$$S_c = n - 1$$

(3.5)

Dónde:

$S_c$ : Número de señales portadoras necesarias.

n: Número de niveles en el voltaje de salida.

En la técnica de modulación PWM con disposición alterna opuesta de fase, las señales portadoras adyacentes se encuentran desplazadas un nivel de CD positivo o negativo y desfasadas 180° con respecto a la señal portadora adyacente [47]. La señal portadora  $V_{p1}$  se obtiene a partir de la ecuación (3.6). Como regla general, el valor de la amplitud de todas las señales portadoras debe ser igual, por lo tanto,  $A_{p1} = A_{p2} = A_p$ . Las demás señales portadoras se encuentran desplazadas un nivel de CD positivo o negativo respecto a la señal  $V_{p1}$ , según sea el caso.

$$V_{p_1} = A_p \left[ \frac{2}{\pi} \arcsin \left( \sin \left( 2\pi f_p t - \frac{\pi}{2} \right) \right) \right]$$

(3.6)

Dónde:

$A_p$ : Amplitud de la señal portadora triangular (Volts, V).

$f_p$ : Frecuencia de la señal portadora triangular (Hertz, Hz).

t: Tiempo (segundos, s).

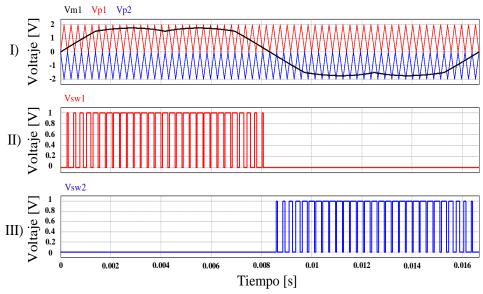

En la Figura 3.2 se muestran las señales portadoras y moduladora para la fase A, así como las señales PWM para los interruptores de potencia. Los parámetros utilizados son: m=0.9 y  $f_m$ =60. La técnica de modulación aplicada es una combinación de ambas técnicas explicadas anteriormente y en lo sucesivo se le denominará CBSV-PWM.

**Figura 3.2.** Señales utilizando la modulación CBSV-PWM. I) Señales portadoras y moduladora para la fase A y II) Señales de comando para los DSeP

## 3.3 Descripción del código

La técnica de modulación descrita en la sección anterior, se implementó en una tarjeta FPGA Altera Cyclone II EP2C5T144, cuyas características y bajo costo la hacen una solución ideal para una amplia gama de aplicaciones, en especial aquellas áreas relacionadas con el procesamiento y generación de señales [9].

En este caso, el uso del FPGA permite generar los estados de encendido y apagado de los 12 interruptores de potencia que integran el inversor. El procedimiento empleado para generar estas señales se divide en dos programas; un *script* de Matlab y un código VHDL creado en el software Quartus II.

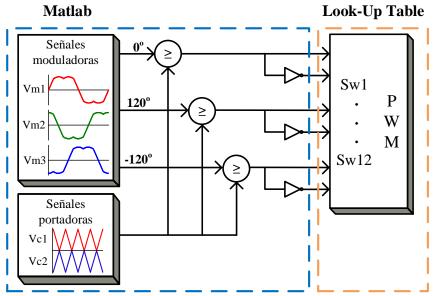

## 3.3.1 Programación en Matlab

En el *script* de Matlab se escriben las ecuaciones presentadas en la sección anterior para generar las señales moduladoras y portadoras. También, se comparan todos los valores de la señal moduladora con los valores de la señal portadora, si la señal moduladora es mayor, la salida del bloque comparador es 1, en caso contrario, la salida es 0. Este número (1 o 0) indica el estado que debe tomar cada señal, estado alto (encendido) cuando el valor es 1 o estado bajo (apagado) cuando es 0. Finalmente, a la salida del comparador se tienen 6 señales y sus complementos, 12 señales PWM en total. En la Figura 3.3 se muestra el diagrama a bloques de las operaciones que se realizan en el *script* de Matlab.

Los datos de las 12 señales PWM se guardan en una matriz, estos elementos establecen los tiempos y el patrón de conmutación que sigue cada uno de los interruptores durante un ciclo de línea. Los datos de esta matriz también conocida como tabla de búsqueda (LUT, por sus siglas en inglés *Look-Up Table*) se envían y almacenan en un archivo de texto.

Figura 3.3. Esquema del proceso empleado para generar las señales PWM

El uso de una LUT permite ahorrar tiempo de procesamiento, ya que es mucho más rápido recuperar un valor de la memoria que hacer operaciones y cálculos complejos con el FPGA. En este caso, los datos almacenados en la LUT precalculada en Matlab determinan las condiciones de operación del inversor. Es posible tener una o más LUT en el mismo programa para efectuar cambios, por ejemplo, modificar el índice de modulación y obtener un voltaje de salida variable. Esto se puede hacer fácilmente, generando una LUT para cada índice de modulación que se desea obtener.

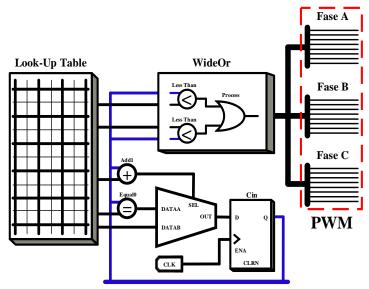

## 3.3.2 Programación en Quartus II

El programa principal es un código escrito en lenguaje VHDL utilizando el software Quartus II. La estructura general de este programa consta de tres etapas:

- 1. Declaración de librerías, parámetros de entrada/salida, constantes y tipo de señales utilizadas en el programa.

- 2. Divisor de frecuencia basado en contadores para generar una señal a una frecuencia determinada, la cual depende de la frecuencia de la señal moduladora y el valor del oscilador con el que dispone el FPGA.

- 3. Bloque con sentencias secuenciales del tipo case, en el cual se utilizan los datos almacenados en el archivo de texto que genera el script de Matlab para enviar las señales de salida, asignando el tiempo en que cada señal está en un estado alto (encendido) o bajo (apagado).

En la Figura 3.4 se muestra el esquema que describe la estructura de este programa, generado por el software Quartus II. Este modelo, comúnmente llamado transferencia lógica de registros (RTL, por sus siglas en inglés *Register Transfer Logic*), describe el programa en términos de cómo los datos se mueven a través de los registros del sistema.

Figura 3.4. Modelo RTL del generador PWM creado en Quartus II

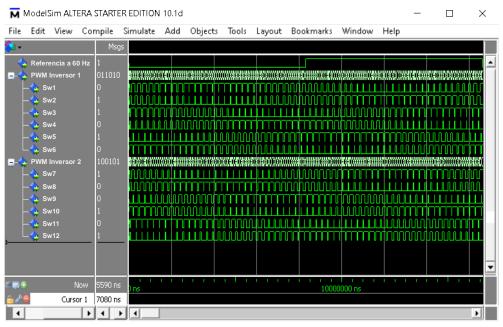

### 3.3.3 Simulación en ModelSim

El siguiente paso es comprobar que el código VHDL funciona y ejecuta correctamente las tareas para las que se diseñó. En la Figura 3.5 se muestran la señal de referencia a 60Hz y las señales PWM obtenidas mediante simulación en ModelSim. En el archivo de la simulación se utiliza un reloj de 20ns, cuyo periodo corresponde a la frecuencia de 50MHz del reloj interno del FPGA.

Figura 3.5. Señales PWM obtenidas mediante simulación en ModelSim

Después de concluir el proceso de diseño y validación del algoritmo, el archivo generado por el software Quartus II, se utiliza para programar el FPGA. El archivo compilado se transfiere al FPGA a través de una interfaz serie (JTAG) mediante el *ByteBlaster* de Altera.

## Capítulo 4. Pruebas y resultados

## 4.1 Descripción general

El uso de convertidores de potencia para el accionamiento de motores de inducción, afecta el desempeño de la máquina debido a las componentes armónicas en los voltajes que entrega el inversor. Distorsiones significativas en las señales de alimentación del motor, pueden provocar un sobrecalentamiento de los devanados, acelerando la degradación del sistema de aislamiento. Además, debido a las altas frecuencias de conmutación utilizadas en los inversores, se incrementan las interferencias de modo común causadas por la capacitancia parasita entre varias partes metálicas del motor y tierra, provocando el flujo de corrientes pulsadas no deseadas; ya que pueden ocasionar daños en los cojinetes, degradar el sistema de aislamiento, aumentar las pérdidas de potencia, incrementar los niveles de ruido acústico y los niveles de vibración.

En definitiva, es importante considerar los efectos perjudiciales que pueden ocasionar el uso de convertidores de potencia en los motores de inducción, con el fin de tomar las medidas apropiadas para prevenir o minimizar los daños causados al motor y garantizar una operación adecuada y segura del conjunto inversor – motor.

En este capítulo se analizan los resultados obtenidos en las pruebas experimentales. En primer lugar, se presenta el funcionamiento del inversor dual con la técnica de modulación CBSV-PWM; posteriormente se compara la eficiencia de ambos inversores con una carga resistiva; y finalmente se evalúa el desempeño del conjunto inversor – motor de inducción trifásico, analizando distintos parámetros, tales como: THD, WTHD, vibraciones, ruido, temperatura y velocidad.

### 4.1.1 Pruebas de la técnica de modulación

Con la finalidad de analizar el funcionamiento del inversor dual con la técnica de modulación CB-SVPWM, se realizaron una serie de simulaciones en el software PSpice®. En la Figura 4.1 se muestra el diagrama de conexión utilizado en las simulaciones. Para estas pruebas se mantuvieron las siguientes condiciones en cada inversor:

- Inversor 1. La técnica de modulación utilizada se mantuvo fija, es decir, la fase A con un ángulo de 0° y las fases B y C a -120° y 120° respectivamente, tomando como referencia la fase A.

- Inversor 2. Se utiliza la misma técnica de modulación utilizada en el inversor 1, con un desplazamiento de fase (α) de 0° a 180° respecto a las fases A, B y C del inversor 1, aumentando en intervalos de 10°.

Figura 4.1. Diagrama de conexión del inversor dual y la técnica de modulación

En la Tabla 4.1 se muestran los parámetros utilizados para las simulaciones. Después de realizar varias pruebas, se eligieron esos valores del índice de modulación y la frecuencia de conmutación, porque presentaron menor contenido armónico en la señal de voltaje.

| Parámetro                   | Valor    |  |

|-----------------------------|----------|--|

| Voltaje de entrada (VCD)    | 155 V    |  |

| Resistencia de carga (R)    | 15.6 Ω   |  |

| Frecuencia de portadora     | 3.6 kHz  |  |

| Frecuencia de moduladora    | 60 Hz    |  |

| Índice de modulación        | 0.9      |  |

| Tiempo de simulación        | 50 ms    |  |

| Ángulo de desfasamiento (α) | 0 – 180° |  |

Tabla 4.1. Parámetros utilizados en simulación

Para las pruebas experimentales se mantuvieron las mismas condiciones que en las simulaciones, es decir, se evaluó el comportamiento del voltaje en los terminales  $V_{AA'}$  con la técnica de modulación CBSV-PWM, desfasando el inversor 2 con respecto al inversor 1. Se realizaron 18 pruebas en total. Cada prueba tardó aproximadamente 5 minutos, entre configurar y cargar el programa en el FPGA y realizar las mediciones correspondientes. Debido a que solo se desea evaluar el funcionamiento del inversor dual con la técnica de modulación, en lugar del motor, en estas pruebas se utilizó una carga resistiva compuesta por 3 lámparas incandescentes de 75 W.

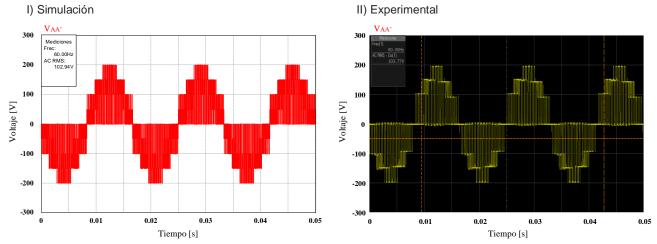

En la Figura 4.2 se muestra el voltaje  $V_{AA'}$  obtenido en simulación y de manera experimental, cuando el inversor 2 tiene un desplazamiento de fase de 180° con respecto al inversor 1. Se puede observar que la forma de onda es similar a la obtenida con la conexión en estrella debido al neutro que se genera a través del inversor 2. De manera que, cuando se tiene la conexión con devanados abiertos el voltaje fase-neutro del motor ( $V_{FN}$ ) está dado por la siguiente ecuación:

$$V_{FN} = V_{AA'} = V_A - V_{A'} \tag{4.1}$$

Como consecuencia, al desfasar el inversor 2 con respecto al inversor 1 un ángulo  $\alpha$  igual a 180° se tiene una configuración en estrella, con la diferencia de que en este caso el voltaje del bus de CD se divide en 2 fuentes de menor valor, permitiendo generar un voltaje de salida alterno con más niveles de volta escalonados utilizando 2 inversores tradicionales.

**Figura 4.2.** Voltaje  $V_{AA'}$  obtenido con un desfasamiento de 180°

Los voltajes fase-fase del sistema ( $V_{FF}$ ) son virtuales (voltajes equivalentes que no se pueden obtener mediante medición directa), pero son útiles porque de ellos se puede calcular el voltaje en los devanados del motor, el cual es igual al de la conexión estrella con la modulación adecuada. Entonces, cuando se tiene la configuración dual, el voltaje fase-fase, se puede calcular con la ecuación (4.2) [29, 45]:

$$V_{AB_{motor}} = (V_A - V_B) - (V_{A'} - V_{B'})$$

(4.2)

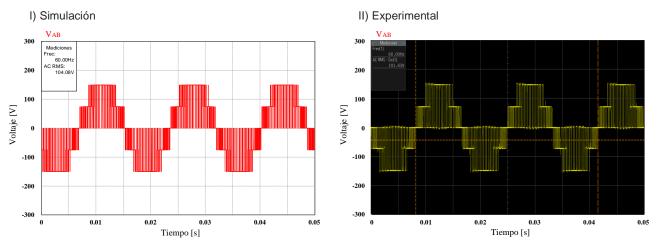

En la Figura 4.3 se muestra la forma de onda del voltaje  $V_{AB}$  a la salida del inversor 1 en simulación y experimental, se obtiene una forma de onda de cinco niveles mediante esta técnica de modulación que generalmente se utiliza para obtener tres niveles.

**Figura 4.3.** Voltaje  $V_{AB}$  obtenido con un desfasamiento de 180°

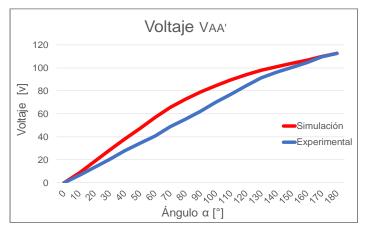

En la Figura 4.4 se muestra el voltaje medido en los terminales de la carga ( $V_{AA}$ ) con un desplazamiento de fase de 0° a 180° obtenido en simulación y de manera experimental, utilizando la técnica de modulación CBSV-PWM. Como se puede observar, en el intervalo que va desde 20° a 180°, existe una diferencia de hasta 15V entre el voltaje obtenido en simulación y el voltaje obtenido experimentalmente, esto se le atribuye a que en simulación se consideraron a los componentes como ideales, principalmente los dispositivos IGBT. No obstante, en ambos casos el comportamiento es el mismo, es decir, el voltaje aumenta conforme el ángulo de desfasamiento es mayor, alcanzando un voltaje máximo de 117 V cuando se tiene un desfase de 180°. En las pruebas experimentales el voltaje obtenido a la salida del inversor es directamente proporcional al ángulo de desfasamiento entre el inversor 1 y el inversor 2. De manera que, es posible controlar el voltaje con el que se alimenta el motor, manteniendo una relación lineal entre estos dos parámetros.

**Figura 4.4.** Voltaje  $V_{AA'}$  en función del ángulo de desfasamiento ( $\alpha$ )

Tomando en cuenta los resultados obtenidos en las pruebas con la técnica de modulación, para las siguientes pruebas se decidió tomar solo el punto de operación que proporciona mayor voltaje a la salida del inversor dual, es decir, cuando se tiene un ángulo de desfasamiento de 180° entre ambos inversores.

#### 4.1.2 Pruebas de eficiencia